# SVR ENGINEERING COLLEGE

- Service Virtue Reverence

AYYALURU METTA, NANDYAL, KURNOOL (DIST.) - 518503 (Approved by AICTE, New Delhi & Permanently Affiliated to JNTUA, Anantapuramu)

SVR Engineering College has initiated an innovation ecosystem to inculcate research activities among students and faculty members.

### A NOVEL LOW COST WEARABLE SENSOR USING VELOSTAT:

The Speech recognition technology is continuously improving which is making way for innovative ideas to come up. This technology is widely used and implemented across various platforms. The communication between the human speech and the computer application which recognize the speech is only possible by interfacing.

Velostat is a low-cost, low-profile electrical bagging material with piezoresistive properties, making it an attractive option for in-socket pressure sensing. The focus of this research was to explore the suitability of a Velostatbased system for providing real-time socket pressure profiles. The prototype system performance was explored through a series of bench tests to determine properties including accuracy, repeatability and hysteresis responses, and through participant testing with a single subject.

PRINCIPAL SVR ENGINEERING COLLEGE AYYALUR (V), Nandyal (Dist), A.P., 518 502

## SVR ENGINEERING COLLEGE

- Service Virtue Reverence -

AYYALURU METTA, NANDYAL, KURNOOL (DIST.) – 518503 (Approved by AICTE, New Delhi & Permanently Affiliated to JNTUA, Anantapuramu)

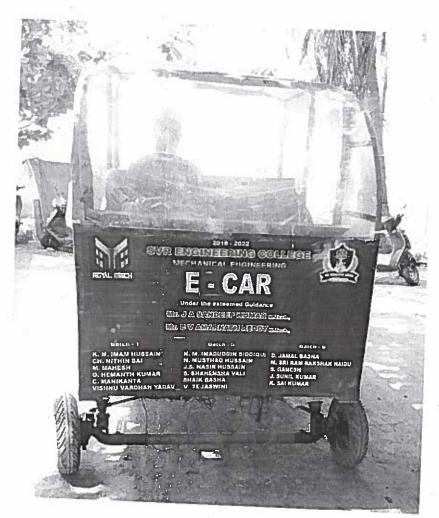

### Battery Electric Vehicle: An Emerging Technology:

As concerns of oil depletion and security of supply remain as severe as ever, and faced with the consequences of climate change due to greenhouse gas emissions, India and other European countries increasingly looking at alternatives to traditional road transport technology. Battery electric vehicle as seen as promising technology, which could lead to the decarbonisation of the light duty vehicle fleet and to independence from oil.

PRINCIPAL

SVR ENGINEERING CO!

# SVR ENGINEERING COLLEGE

– Service Virtue Reverence -

AYYALURU METTA, NANDYAL, KURNOOL (DIST.) - 518503 (Approved by AICTE, New Delhi & Permanently Affiliated to JNTUA, Anantapuramu)

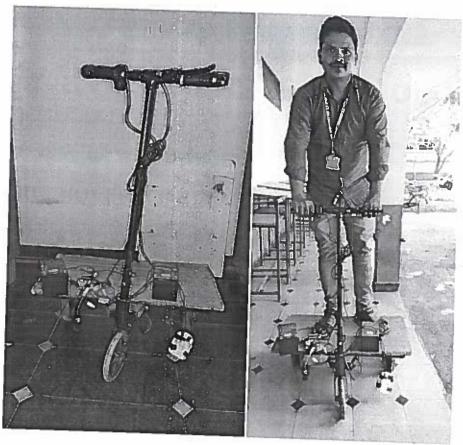

#### **ELECTRIC HOVERBOARD:**

A hoverboard has two large wheels separated by a long board and it is powered by electricity through battery. The hover board allows riders to move across the ground without pedalling or pushing with their feet.

PRINCIPAL SVR ENGINEERING COLLEGE AYYALUR (V), Nandyal (Dist), A.P.:518.502 (12) PATENT APPLICATION PUBLICATION

(19) INDIA

(22) Date of filing of Application :20/09/2022

(21) Application No.202211053618 A

(43) Publication Date: 07/10/2022

(54) Title of the invention: SYSTEMATIC FRAMEWORK FOR SMARTER CONSTRUCTION TECHNIQUES THROUGH ACCOMPLISHING GREEN BUILDING INITIATIVE WITH ZERO WASTE MANAGEMENT

A61F0013150000, B01D0061020000, G06Q0050080000, (51) International classification C02F0001440000, E04C0002040000 (86) International Application No. NΛ Filing Date (87) International Publication No (61) Patent of Addition to : NA :NA **Application Number** Filing Date (62) Divisional to Application NA Number Filing Date

(71)Name of Applicant:

I)ER. PRAFULL KOTHARI

Address of Applicant (ASSISTANT PROFESSOR, DEPARTMENT OF CIVIL ENGINEERING, INSTITUTE OF ENGINEERING AND TECHNOLOGY, MOHANLAL SUKHADIA UNIVERSITY, 2)Dr.M.CHITTARANJAN 3)A USHA 4)J HARISH 4JI HARISH

5)V R SAI DEVAYANI

6)FRAKASH CM

7)TARUN GEHLOT

9]Dr ABHISHEK VERMA

10)Dr ABHISHEK VERMA

10)Dr SHWETA RAN

11)Dr A RAVITIEJA

12)V VENKATA RAMI REDDY

Name of Applicant: NA

(72)Name of Inventor:

1)FR PRAFILLA KOTTHANI DER, PRAFULL KOTHARI Address of Applicant (ASSISTANT PROFESSOR, DEPARTMENT OF CIVIL ENGINEERING, INSTITUTE OF ENGINEERING AND TECHNOLOGY, MOHANLAL SUKHADIA UNIVERSITY. 2)DE.M.CHITTARANJAN

Address of Applicant PROFESSOR & HEAD, SRI VENKATESWARA COLLEGE OF

ENGINEERING, TIRUPATI-517507 TIRUPATI Address of Applicant ASSISTANT PROFESSOR, DEPARTMENT OF CIVIL ENGINEERING, SRI VENKATESWARA COLLEGE OF ENGINEERING, TIRUPATI TIRUPATI

5) V R SAI DEVAYANI 5)V R SAI DEVAYANI Address of Applicant: ASSISTANT PROFESSOR, DEPARTMENT OF CIVIL ENGINEERING, SRI VENKATESWARA COLLEGE OF ENGINEERING, TIRUPATI, PIN:517501 TIRUPATI 6)PRAKASH CM 6)PRAKASH CM

Address of Applicant -ASSISTANT PROFESSOR, DEPT- OF CIVIL ENGINEERING. SREE

VENKATESHWARA COLLEGE OF ENGINEERING, TIRUPATI TIRUPATI

7)TARUN GEHLOT

Address of Applicant -ASSISTANT PROFESSOR ( CIVIL ENGINEERING) COLLEGE OF TECHNOLOGY

AND AGRICULTURE ENGINEERING AGRICULTURE UNIVERSITY JODHPUR RAJASTHAN INDIA Address of Applicant : ASSISTANT PROFESSOR, CIVIL ENGINEERING DEPARTMENT, JAYPEE UNIVERSITY OF ENGINEERING AND TECHNOLOGY, GUNA PIN-473226 GUNA 10)Dr. SHWETA RANI

Address of Applicant :ASSISTANT PROFESSOR, DEPARTMENT OF GEOGRAPHY, DYAL SINGII COLLEGE, UNIVERSITY OF DELHI, LODHI ROAD, NEW DELHI-110003, INDIA NEW DELHI—

Address of Applicant :ASSISTANT PROFESSOR, DEPARTMENT OF CIVIL ENGINEERING, SVR ENGINEERING COLLEGE, AYY ALUR, NANDYAL, KURNOOL, ANDHRA PRADESH, INDIA.

NANDYAL

13)Y VENKATA RAMI REDDY

Address of Applicant :ASSISTANT PROFESSOR, DEPARTMENT OF CIVIL ENGINEERING, SVR

ENGINEERING COLLEGE, AYYALUR, NANDYAL, KURNOOL, ANDHRA PRADESH, INDIA.

NANDYAL

(57) Abstract :

(37) Austract;

Systematic framework for Smarter Construction techniques through accomplishing Green Building initiative with Zero Waste Management is the proposed invention. The proposed invention implements a framework of systematic approach to integrate the green building techniques in construction. The invention aims at achieving zero waste management is the proposed invention. The proposed invention implements a framework of waste and initiate green building.

II)Dr A RAVITHEJA

No. of Pages: 13 No. of Claims: 7

PRINCIPAL

SVR ENGINEERING COLLEGE

AYYALUR (V), Nandyal (Dist); A.P.-518

(12) PATIENT APPLICATION PUBLICATION AIGNI(21)

(21) Application No. 201841036063 A

(22) Date of filing of Application :25/09/2018

(43) Hubblention Date: 05/10/2018

### (54) Title of the invention: A DEVIGE FOR DETECTING SYNTHETIC FOOD INGREDIENTS

| (51) International classification  (31) Priority Document No (32) Priority Date (33) Name of priority country (86) International Application No Filing Date (87) International Publication No (61) Patent of Addition to Application Number Filing Date (62) Divisional to Application Number Filing Date | :A61K35/00;<br>A61K36/00 | (71)Name of Applicant:  1)ALLINNOV RESEARCH AND DEVELOPMENT PRIVATE LIMITED Address of Applicant: D. NO.: 29B, Bairappa Colony, Krishnagiri - 635001, Tamilnadu, India Tamil Nadu India (72)Name of Inventor:  1)Dr.MOHD ABDUL BARI 2)Dr.J.B.V.SUBRAHMANYAM 3)Dr.G.VIJAYA 4)Dr.K.VENKATESH SHARMA 5)Dr.S. CHIDAMBARANATHAN 6)MD. RAFEEQ 7)BETALA RAKESH 8)Dr. POTLURI SANKAR BABU 9)KORRA SEENA NAIK 10)K.S.R.K.SARMA 11)Dr.SUDARSHAN.E 12)DR.CHANDRASHEKHAR.A 13)SHANKARNAYAK BHUKYA |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Present invention relates to a device for detecting synthetic food products. More particularly, the invention relates to a device for detecting synthetic rice and egg. Moreover, the device is designed to automatically connect to a smart electronic device for cooking rice and egg. The device comprises of a pressure applying chamber for detecting of synthetic grains and furthermore, an imaging plate No. of Pages: 16 No. of Claims: 8

PRINCIPAL SOLLEGE AYYALUR (V), Nandyal (Blat), A.P.-519 502

(43) Publication Date: 18/09/2020

# (54) Title of the invention : AN EFFICIENT ARITHMETIC VLSI ARCHITECTURE FOR DWPT BREOR APPROXIMATION

| (51) International classification  (31) Priority Document No (32) Priority Date (33) Name of priority country (86) International Application No Filing Date (87) International Publication No (61) Patent of Addition to Application Number Filing Date (62) Divisional to Application Number Filing Date | :H03H0017060000,<br>H03H0017020000,<br>G06F0007544000,<br>G06F0017500000<br>:NA<br>:NA<br>:NA<br>:NA<br>:NA<br>:NA<br>:NA<br>:NA<br>:NA | (71)Name of Applicant:  1)Mahesh Enumula Address of Applicant: Flat no 304, Anco height apartments, Bandlaguda Jagir, Hyderabad. PIN.500086 Phone no: 9912438444 B-Mail: researcher mahesh@gmail.com Telangana india (72)Name of Inventor:  1)GADDAM RENUKA 2)Dr. V. Usha Shree 3)Dr.P.Chandrasekhar Reddy 4)Dr. Molakatala Nagamani 5)Dr. Sasi Kiran Jangala 6)Dr.S.M.K.M ABBAS AHMAD 7)Dr.Sankar babu Potluri, 8)JYOTHI. CHINNA BABU 9)Prof. D SURENDRA RAO 10)Prof. V.BHAGYA RAJU 11)S.Hemanth chowdary 12)Ravinder Korani 13)MAHESH ENUMULA |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                           |                                                                                                                                         | 13)MAHESH ENUMULA 14)T SYED AKHEEL 15)Mude Sreenivasulu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

(57) Abstract

The power budget, size and cost make the task difficult to integrate more functions as the signal processing algorithms such as Discrete wavelet transform (DWT), Discrete wavelet packet transform (DWPT), finite impulse response (FIR) filtering. Therefore, developing low-complexity hardware efficient arithmetic design for healthcare application remains a challenge. DSP algorithms are implemented in dedicated hardware system to meet space-time requirement of resource constrained applications such as repetitive multiply-accumulate operations, computational symmetry and redundancy. Efficient implementation of multiplication operations is a key issue in digital filter design of DSP application. Separate approach is used for signed and unsigned multiplication. Approximate multiplication and addition operation provide small area and leakage power due to saving of storage data-bits. Approximation computation methodology produces dynamic power reduction due to memory access saving. Approximate computation consider small percentage of accuracy loss that does not affect much the overall application specific performance in digital arithmetic hardware design. Delay and power consumption is considered to be major issue in ripple carry adder (RCA) design is required to study the Mectiveness of the arithmetic coefficient approximation method on DWPT computation. The bit level optimization of full-width adder tree for multiple constant multiplication (MCM) is given to taking the advantage of shifting operation. Considered images with different colour and edge information for DWPT applications are grouped as low-texture, moderate-texture and higher-texture images for discussion purpose. Less colour variation with less edge information refer to low-texture image, less colour variation with more edge information refer to moderate-texture image, and more colour variation with more edge information refer to higher-texture image. Pixel variation is more in data-vectors of higher-texture images, relatively less in data-vectors of moderate-texture images and almost absent/small in data-vectors of low-texture images. The proposed shift-add register (SAR) and approximate arithmetic architecture designs use a fixed-bias for error-compensation. The fixed-bias compensates truncation error near accurately for input data-vector with more pixel variation while overcompensate the truncation error for input data-vector with small pixel variation.

No. of Pages: 15 No. of Claims: 2

PRINCIPAL SVR ENGINEERING COLLEGE The Patent Office Journal No. 38/2020 Dated 18/09/2020 Nandyal (Dist), A.P. 1.2 502 41014

#### HEIPATENT APPLICATION FUNCATION HE INTERA

A Date of Application 09 08 4030

\$217 Application for 2020 4100 \$347 A

(Ad) Poblishimm Danie (14 apr 202)

i)Mr. NMD JUHAIR BASHA (ASSOCIATE PROVESSOR) Addition of Applicant DEPARTMENT OF CHE KAULAM

9)Dr. CH SUBRAHMANYAM (PROFESSOR) 10)Dr. V BHAGYA RAJU (PROFESSOR) 11)Dr. M SRINIVASULU (PROFESSOR & HQD)

(71) Name of Applicant

THE OF BILLINGS TO CHEDIT CARD FRAUD DEFINCTION INTELLIGIBN'S PROCESS TO CHEDIT CARD FRAUD DETECTION USING DEEP LEARNING, MACHINIC LEARNING

| (51) International classification (4) Priority Document No 12) Priority Date (33) Name of priority country (85) International Application No Filing Date (87) International Publication No (61) Parent of Addition to Application Number Filing Date (62) Divisional to Application Number Filing Date | :NA<br>:NA | Addition of Applicant Department of the Raukami HARANADHAREDDY HISTITUTE OF TECHNICOGY, GUSTOR HARANADHAREDDY HISTITUTE OF TECHNICOGY, GUSTOR 1522019, A.P., RIDIA E main membering grant come and may 1 Dr. K VENKATA SUBBA REDDY (PROPESSOR & HOD); 3 Dr. MD UMAR KHAN (PROFESSOR) 4 Dr. B TARAKESWARA RAO (PROFESSOR) 5 Dr. K V RAMPRASAD (PROFESSOR) 6 Dr. SAKHAMURI SURYANARAYANA (PROFESSOR) 7 DMr. CHILLARA ESWARA KUMAR (ASSISTANT) PROFESSOR) 8 Dr. J SRINIVAS (ASSISTANT PROFESSOR) 10 Dr. V BHAGYA RAJU (PROFESSOR) 11 Dr. M SRINIVASULU (PROFESSOR) 12 Dr. SANKAR BABU POTLURI (PROFESSOR) 12 Dr. K VENKATA SUBBA REDDY (PROFESSOR) 2 Dr. K VENKATA SUBBA REDDY (PROFESSOR) 3 Dr. MD UMAR KHAN (PROFESSOR) 5 Dr. K VENKATA SUBBA REDDY (PROFESSOR) 5 Dr. K V RAMPRASAD (PROFESSOR) 6 Dr. B TARAKESWARA RAO (PROFESSOR) 6 Dr. SAKHAMURI SURYANARAYANA (PROFESSOR) 7 DMr. CHILLARA ESWARA KUMAR (ASSISTANT) PROFESSOR) 8 Dr. J SRINIVAS (ASSISTANT PROFESSOR) 9 Dr. CH SUBRAHMANYAM (PROFESSOR) |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### (57) Abstract :

12)Dr. SANKAR HABU POTLURI (PROFESSOR ABSTRACT My invention Credit Card Fraud Detection is a intelligent system and process to detects fraudulent transactions using a melligent predictive model such as a deep learning programming, neural network to evaluate individual customer accounts (through Credit Care) and identify pleastably figurdulent transactions (time maximum 24 H) based on learned relationships, global bank data server among known variables. The invented system may also output reason codes indicating relative contributions of various variables to a particular result and the system periodically (per transaction track the register mobile location and credit card location accordingly detect) monitors its performance and redevelops the model when performance drops below a predetermined level. The invention also give the probability may then be provided as output to a human decisionenaker involved is processing the per transaction with both location matching (credit card, mobile no) or the issuer may be argualed when the probability exceeds a predetermined amount. The effective fraud detection model generally requires more variables than convenie and parameter analysis systems can handle and also in order to cupture new fraud schemes, parameter analysis systems must be redeveloped offers, and automate so of Pages: 28 No. of Claum: 10

PRINCIPAL **SVR ENGINEERING COLLEGE** AYYALUR (V), Nandyal (Dist), A.P.-518 502 (12) PATENT APPLICATION PUBLICATION

(19) INDIA

(22) Date of filing of Application :27/02/2021

(21) Application No.202141008336 A

(43) Publication Date: 05/03/2021

#### (54) Title of the invention: SELF HEALING COMPOSITE

| (51) International classification  (31) Priority Document No (32) Priority Date (33) Name of priority country (86) International Application No Filing Date (87) International Publication No (61) Patent of Addition to Application Number Filing Date (62) Divisional to Application Number Filing Date (57) Abstract: | C0480020100000,<br>C04B00280200001,<br>C04B0111720000,<br>C04B0014020000<br>:NA<br>:NA | (71)Name of Applicant:  1)Dr.T.Chandra Sekhara Reddy Address of Applicant Professor of Civil, Engineering Department, G Pulla Reddy Engineering College, Kurnool- 518007, Andhra Pradesh, India, Andhra Pradesh India 2)Mr.A.Raviteja 3)Dr.C.Sashidhar (72)Name of Inventor: 1)Dr.T.Chandra Sekhara Reddy 2)Mr.A.Raviteja 3)Dr.C.Sashidhar |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

ABSTRACT: Title: Self Healing Composite A self-repairing concrete includes crystalline admixture and silica fume, in which the crystalline admixture and silica fume are mixed for a fixed function of micro-cracks. The quality mixture ratio is: concrete/water=100:1-15:15-50. The manufacturing method is weighing a full amount of water in a container, adding crystalline admixture and silica fume, stirring; pouring the water into the mixing container, adding the corresponding quality of cement; stirring; adding sand and gravel filling materials, conducting worksite watering, volume for each time, vibrating, and air exhausting; until the

No. of Pages: 17 No. of Claims: 10