## **EMBEDDED SYSTEMS**

## B.TECH (IV YEAR – I SEM)

**Department of Electronics and Communication Engineering**

## SVR ENGINEERING COLLEGE NANDYAL.

AYYALURU METTA, NANDYAL– 518 503 (A.P) (Affiliated to JNTUA Anantapur, Approved by AICTE, New Delhi)

### JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY ANANTAPUR B. Tech IV-I Sem. (ECE)

LTPC 3103

#### 15A04702

#### EMBEDDED SYSTEMS

Course Objectives:

• To understand the fundamental concepts of Embedded systems.

• To learn the kernel of RTOS, architecture of ARM processor.

Course Outcomes: After completion the students will be able to

• Design of embedded systems leading to 32-bit application development.

• Understand hardware-interfacing concepts to connect digital as well as analog sensors while ensuring low power considerations.

• Review and implement the protocols used by microcontroller to communicate with external sensors and actuators in real world.

Understand Embedded Networking and IoT concepts based upon connected MCUs

UNIT-I

Introduction to Embedded Systems Embedded system introduction, host and target concept, embedded applications, features and architecture considerations for embedded systems- ROM, RAM, timers; data and address bus concept, Embedded Processor and their types, Memory types, overview of design process of embedded systems, programming languages and tools for embedded design UNIT-II

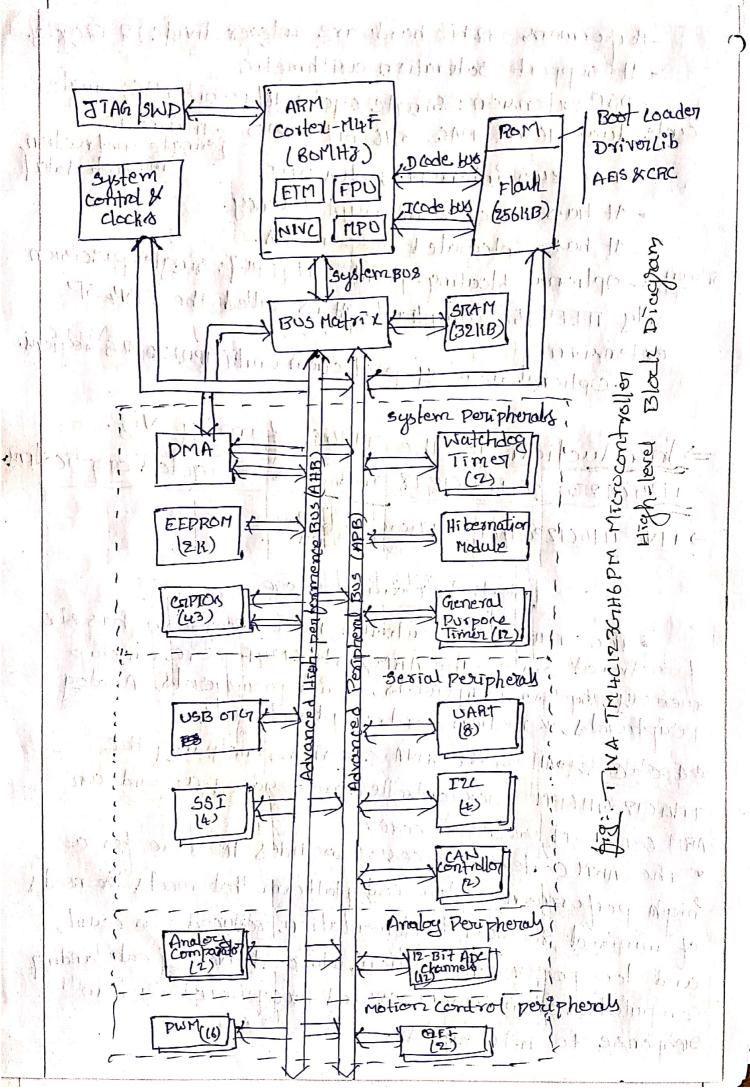

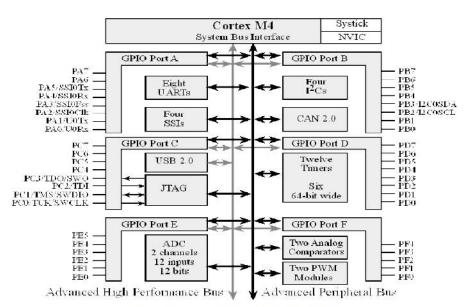

Embedded processor architecture CISC Vs RISC design philosophy, Von-Neumann Vs Harvard architecture. Introduction to ARM architecture and Cortex – M series, Introduction to the TM4C family viz. TM4C123x & TM4C129x and its targeted applications. TM4C block diagram, address space, on-chip peripherals (analog and digital) Register sets, Addressing modes and instruction set basics. UNIT- III

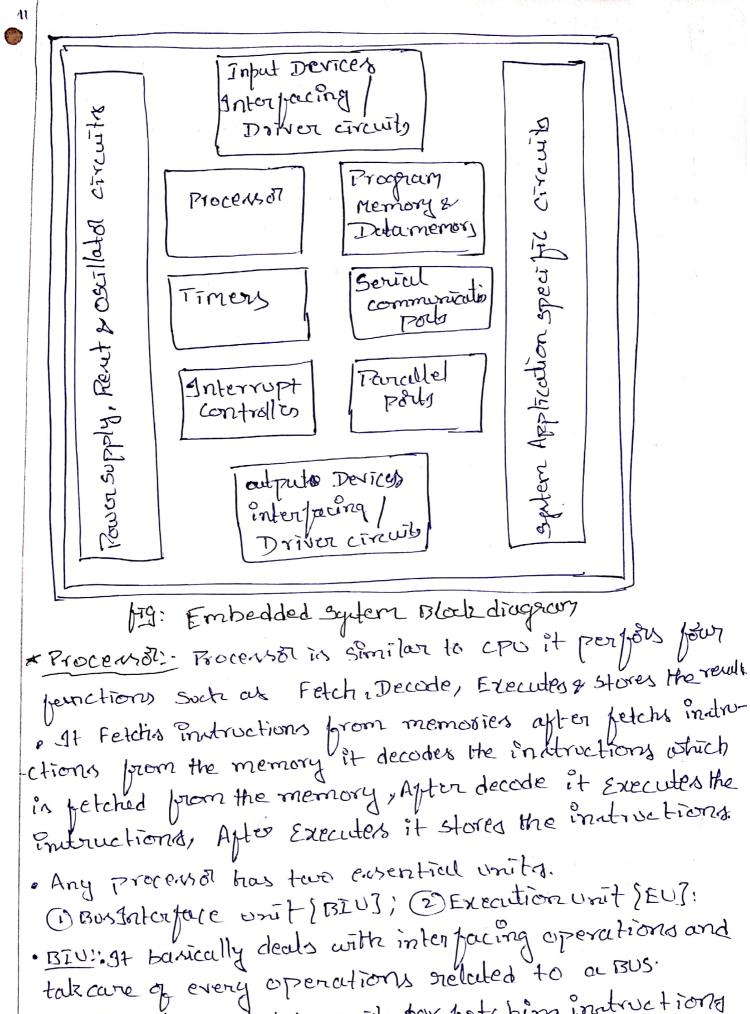

Overview of Microcontroller and Embedded Systems

Embedded hardware and various building blocks, Processor Selection for an Embedded System , Interfacing Processor, Memories and I/O Devices, I/O Devices and

I/O interfacing concepts, Timer and Counting Devices, Serial Communication and Advanced I/O, Buses between the Networked Multiple Devices.Embedded System Design and Co-design Issues in System Development Process, Design Cycle in the Development Phase for an Embedded System, Uses of Target System or its Emulator and In-Circuit Emulator (ICE), Use of Software Tools for Development of an Embedded System Design metrics of embedded systems - low power, high performance, engineering cost, time-to-market.

UNIT-IV

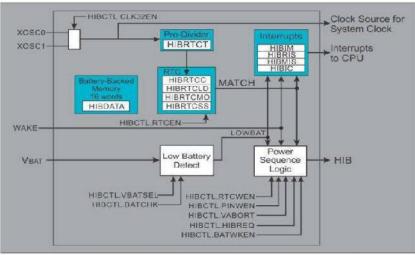

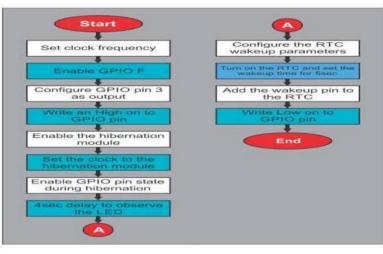

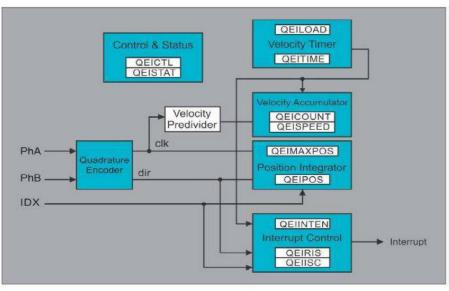

Microcontroller fundamentals for basic programming I/O pin multiplexing, pull up/down registers, GPIO control, Memory Mapped Peripherals, programming System registers, Watchdog Timer, need of low power for embedded systems, System Clocks and control, Hibernation Module on TM4C, Active vs Standby current consumption. Introduction to Interrupts, Interrupt vector table, interrupt programming. Basic Timer, Real Time Clock (RTC), Motion Control Peripherals: PWM Module & Quadrature Encoder Interface (QEI).

Unit-V

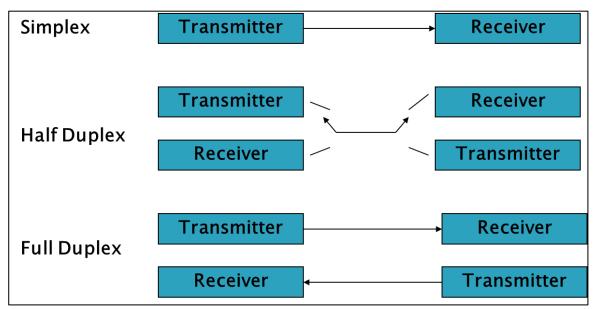

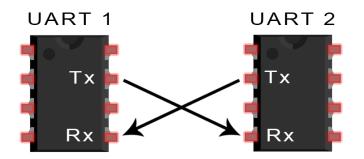

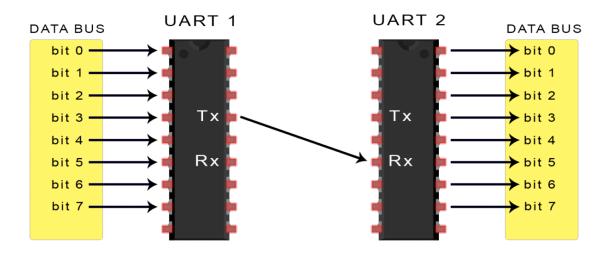

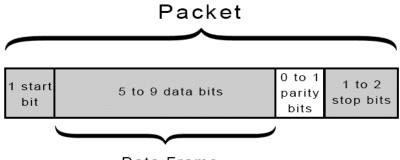

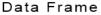

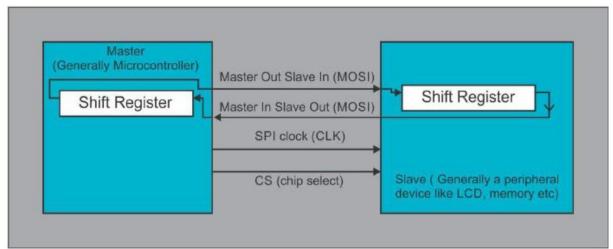

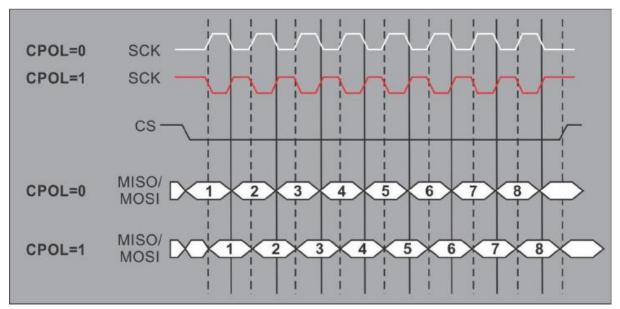

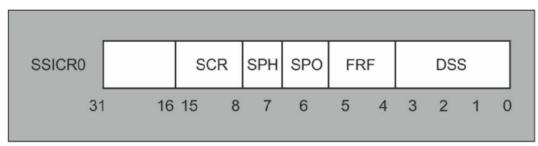

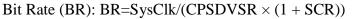

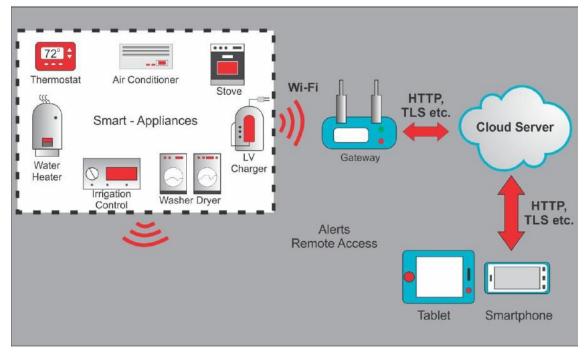

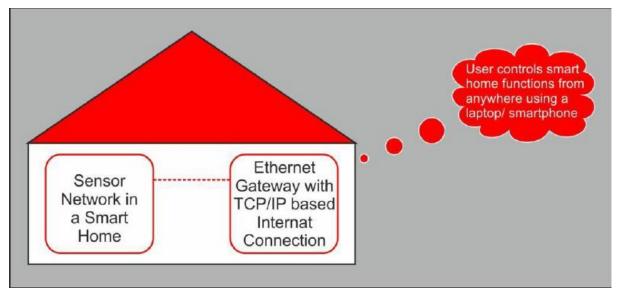

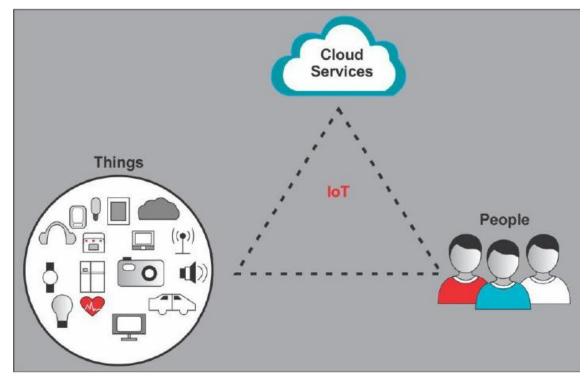

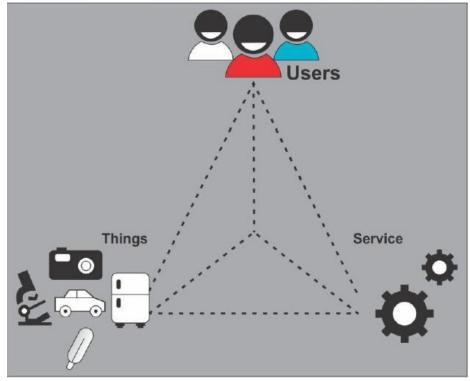

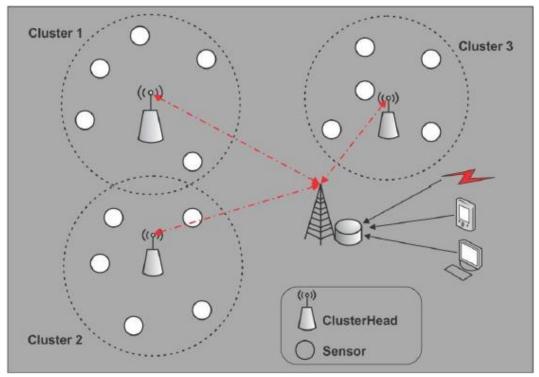

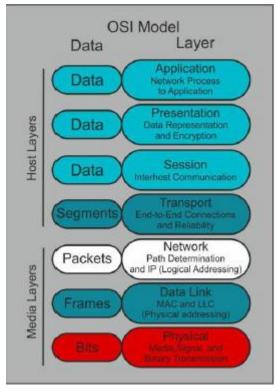

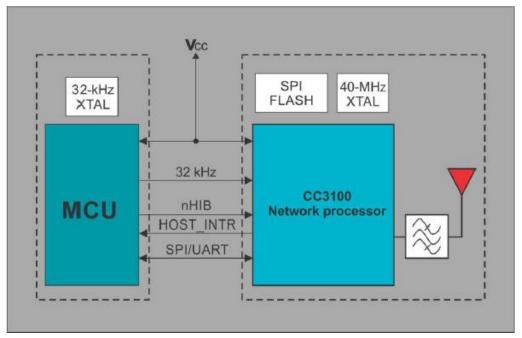

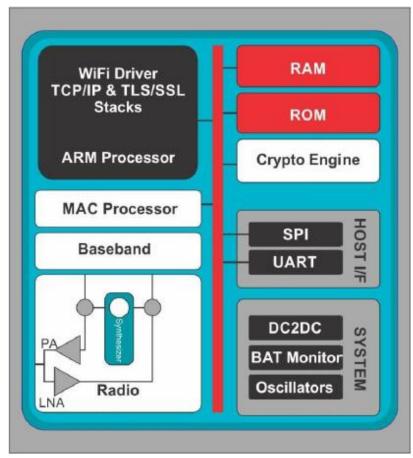

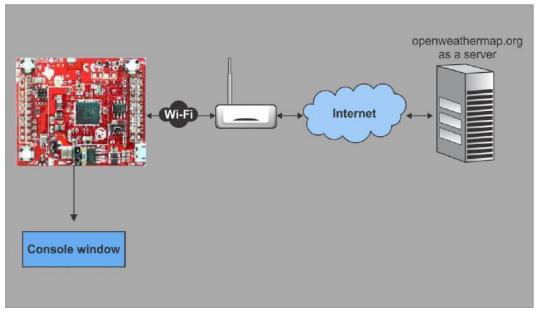

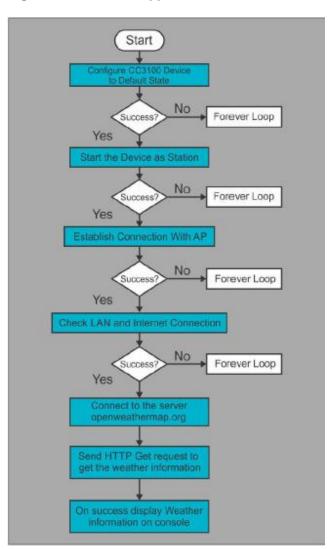

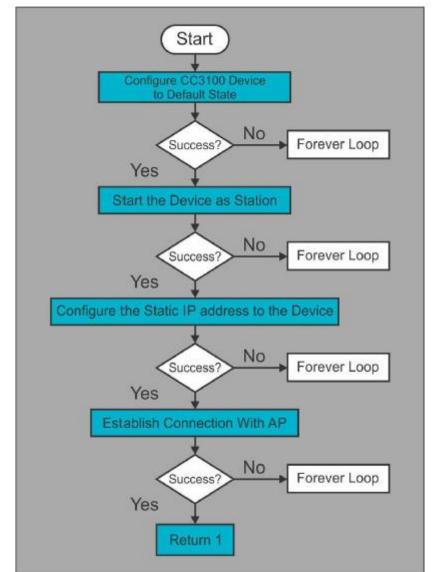

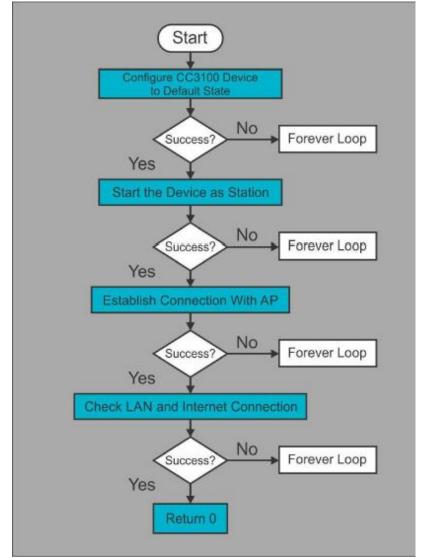

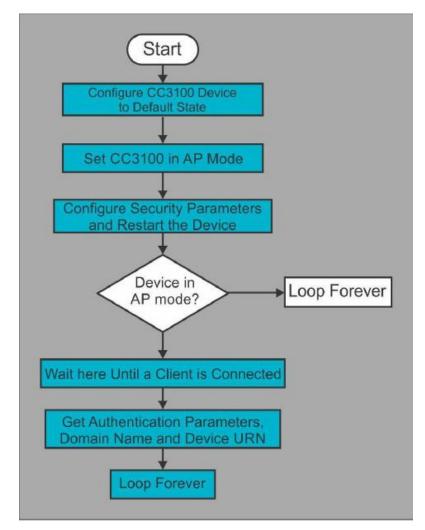

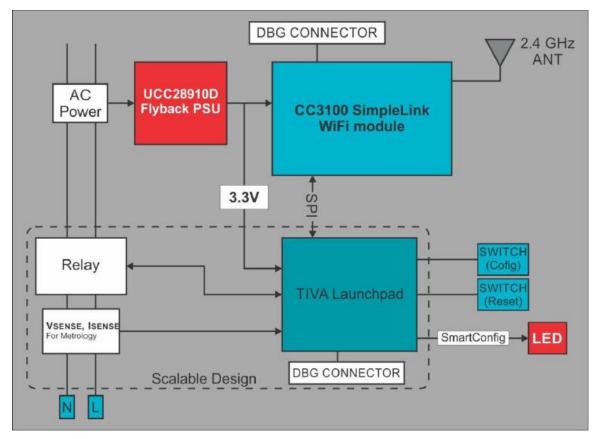

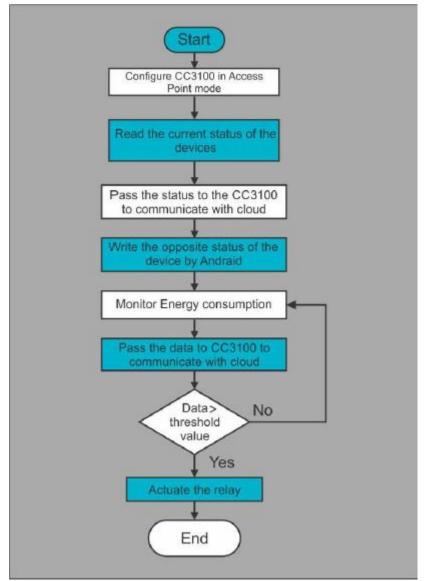

Embedded communications protocols and Internet of things Synchronous/Asynchronous interfaces (like UART, SPI, I2C, USB), serial communication basics, baud rate concepts, Interfacing digital and analog external device, Implementing and programming UART, SPI and I2C, SPI interface using TM4C.Case Study: Tiva based embedded system application using the interface protocols for communication with external devices "Sensor Hub BoosterPack" Embedded Networking fundamentals, IoT overview and architecture, Overview of wireless sensor networks and design examples. Adding Wi-Fi capability to the Microcontroller, Embedded Wi-Fi, User APIs for Wireless and Networking applications Building IoT applications using CC3100 user API. Case Study: Tiva based Embedded Networking Application: "Smart Plug with Remote Disconnect and Wi-Fi Connectivity" Text Books:

1. Embedded Systems: Real-Time Interfacing to ARM Cortex-M Microcontrollers, 2014, Create space publications ISBN: 978-1463590154.

2. Embedded Systems: Introduction to ARM Cortex - M Microcontrollers, 5th edition

Jonathan W Valvano, Createspace publications ISBN-13: 978-1477508992

3. Embedded Systems 2E Raj Kamal, Tata McGraw-Hill Education, 2011 ISBN-

4. 0070667640, 9780070667648

References:

1. http://processors.wiki.ti.com/index.php/HandsOn\_Training\_for\_TI\_Embedded\_Processors

2. http://processors.wiki.ti.com/index.php/MCU\_Day\_Internet\_of\_Things\_2013\_Workshop

3. http://www.ti.com/ww/en/simplelink\_embedded\_wi-fi/home.html

4. CC3100/CC3200 SimpleLink<sup>™</sup> Wi-Fi® Internet-on-a-Chip User Guide Texas Instruments Literature Number: SWRU368A April 2014–Revised August 2015.

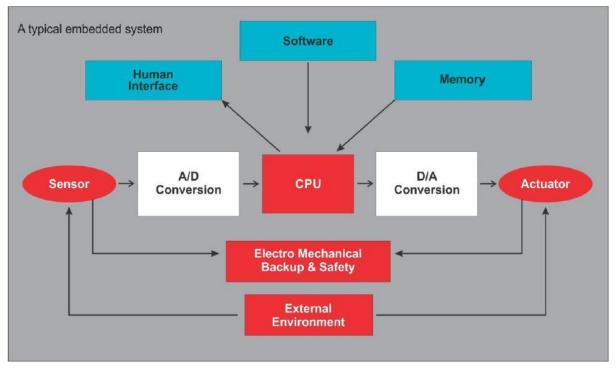

# EMBEDDED SYSTEMS

INIT-I Introduction to Embedded system =) Embedded system introduction:-System: - It is an arrangement for which all its units, assembled work together according to set of rules Ez: "Weitch" is a time displaying system. \* Embedded system:-Dep: () It is a combination of s/w & H/w, which is derigned to perform a particular task and that task has to be completed in a given time. · An embedded system is a combination of hardware and software with some attached peripherals to performa specific task & a narrow range of tasks with restricted resources. . It is an electronic system that is not directly programmed by the user, untike a personal computer. Ez: Mobile phone, Washing machine Microbaure over, Digital cameras, Air conditions etc. · Generic block diagram of an embedded system is Powersuppy 1 Imput device output + controller Frequency generato fil: generic block diagram of an embedded system · Every embedded system convists of certain imput devicer

such as: key boards, switches, sensors, actuations; output devices such as : displays, buzzens. sensors; Processola along with a control program embedded in the off-chip of on-chip memory, and a real time operating system (RTOS). \* characteristics of an Embedded system: • The important characteristics of an embedded system · speed (bytes [sec) : should be high speed · Power (watts) : Lous power divisipation · Size and weight : As for as powible small in size & lous userent. · Accuracy (% error): Must be very accurate · Adaptability : High adaptability and accessibility. · Reliability : Must be reliable over a long period of time. So, an embedded system must perform the operations at a high speed so that it can be readily used for real time applications and its paver consumption must be very low and the size of the system should be as for as parsible small and the readings must be accurate with minimum error. The system must be adaptable for different situations. \* classifications of Embedded Systems: · Embedded System can be clarkified into the following categories based on their functional & performance / size requirements.

Embedded system (E-5) Performance size Functional -Small scale E-S -standalone E-S - Medium scale E-5 - Real time E-3 Hard RTES - Lange scale E-S L-SOFT PLTES Sophistcated E-S - Networked - Mobile + standalone E-S'. • A stand-alone embedded system works by itself. •It is a self-contained device which does not require any host system like a computer. · It takes digital or analog inputs from its input poil, Calibraters, converts, and processes the data, and outputs the resulting data to its attached of device · Which either displays date, of controls and drives the áttached devices. Ex: Jemperature measurement systems, video game consoles, MP3 players étc. \* Real Time Embedded Systems: . An embedded system which gives the required adput in a specified time of which strictly follows the fime deadlines for completion q a task is known as a Real time system. · A Real Time System, in additional to functional Correctness, also satisfics the time constraints. . There are two types of Real time systems

(1) Hard Real-Time system (2) Soft Real-Time system () Hard Real-Time System:-· A Real time system the complection of an operation after its deadline may lead to a critical failure and loss quife or property damage is known as a Hurd · These systems usually interact directly with physical hardware instead of through a human being. • The hardware and software of hard-Real time system must allow a worst case creation [WCET] analysis that guarantees the execution be completed within a . The chip selection and RTOS selection become impostant Strict deadline. factors for hard real-time system deugen. En: Deadline in a mirrile control contredded system Delayed alarm during a Gas leakage, concurbay control system, A delayed response in pacemateris, Failure in RADAR functioning etc. (2) Sout Real-Time system: · A Real time system the complection of an operation after its deadline will cause only the degraded quality, but the system can continue to operate is known as a Solt real time system. . In soft real-time systems, the derign focus is to offer a guaranteed bandwidth to each real-time task and to distribute the resources to the tasks-Er: A Microwave oven, washing machine, TV remote etc.

3 Networked Embedded Systems:-

. The networked embedded systems are related to a network with network interfaces to access the resources. The connected network can be a Local Area Network (LAN) or a Wide Area Network (NAN), or the Internet. The connection can be either . The networked embedded system is the fastert growing area in embedded systems applications. Ex: A home security system is an example of a LAN networked embedded system where all Bensor's are wired, and ronning on the TCP/IP protocol [[3] gatemet Protocol] \* Mobile Embeddied Systems: -• The Postable embedded devices like mobile and cellular phoners, digital cameras, MP3 players, PDA [Personal Digital Assistants) are the example for mobile embedded systems. • The basic limitation of these devices is the limitation of the memory and other resources. \* Based on the performance of the UC they are also classified into 1. Small scaled Embedded System 2- Medium Scaled Embedded system s-Large scaled Embedded system + Small Scaled Empedded System:-• These systems are derigned with a single 8- 37 16 bit MC; they have little handware & software complexities and involve bound-level derigh. They may even be a battery operated systems . When developing embedded s/w for these, an editor, astembler and cross assembler, specific to the MC of UP used, we the main programming tools. · Unully, c is used for developing these systems. Cpigg compilation is done inthe the aviembly, and executable codes are then appropriately located in the system memory.

The software has to fit within the memory available

and heep in view the need to limit power dimipution when system is running continuously. \* Medium Scaled Embedded System:-

- These systems are usually derigned with a single of few 16 - or 32-bit microcontrollers or DSPs or Reduced Instruction set computers (RISCS).

- . These have both trandware and software complexities. They can essentially required of an operating system for complex software design.

- complex software derign. • For complex software derign, there are some programming tools: RTOS, Source code engineering tool, Simulator, Debugger and Integrated Development Environment (IDE). • Software tools also provide the solutions to the hardware

- complexities. These systems may also employ the readily avoilable ASSPS and IPS for the various ponctions.

- \* Large Scaled BI Sophisticated Embedded Systems

- \* These systems are usually derigned with a high End Microcontrollers.

- Sophisticated Embedded systems have enormous handware and software complexities and may need scalable processors of configurable processors and programmable logic arrays.

- · Some of the functions of the hardware resources in the system are also implemented by the software.

- · Development tools for these systems may not be readily available at a reasonable cont or may not be available at all.

Examples: -

SSEM: remportatore maisorement systems, Robotic arm controller, Automatic. chacolate vending machine, stepper motor controllers for a Robotic Arm controller, Digital multimeter etc.

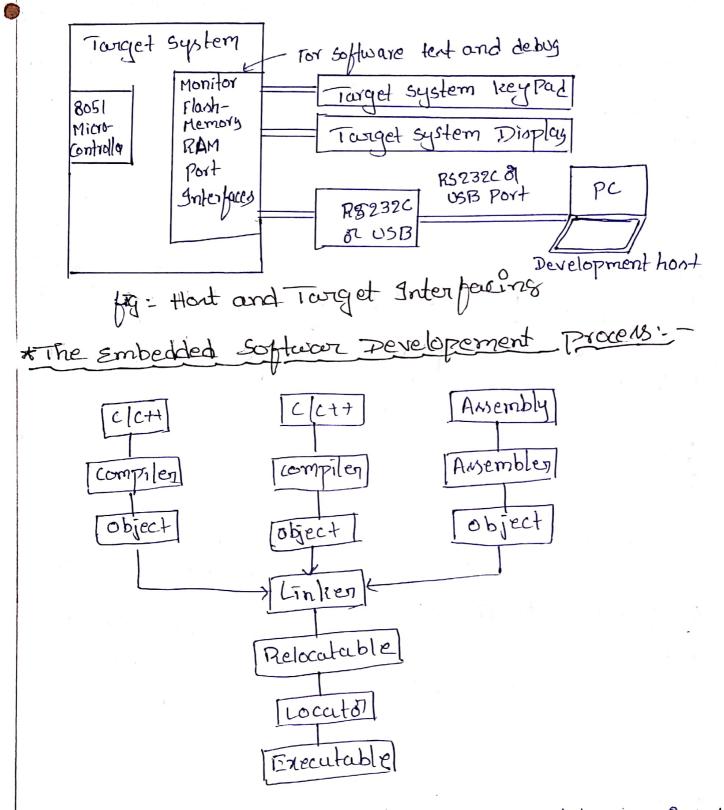

MSES: - Router, nuric systems, ATM machine, Pagez, Fuz machine etc... LSES: - Smart Phones, Multimedia systems. => Host and Target concept:-· Embedded system has derigned to perform specific functions such as computer hardware, softwar and other parts. other parts. . The Embedded system has unique characteristics. File components and punctions of hardward & Soptware can be different for each system. · Now a days. The Embedded software used in all electronic devices such as watches, collular phones etc. . This Embedded Software is similar to general programing · But the embedded handware is unique. - The method of communication between interfaces can be vary from processor to processor. - At leads to more complexity of software - Engineers need to be cusure of the software developing process and tools for Embedded System. • There are a lot of things that software development tods cando automatically when the target platform is well defined . This automation is possible because the tools can exploit features of the hardware and operating system on which your program will execute · Embedded software development tools can rerely make assumptions about the target platform. Hence the user has to provide some explicit instructions of the system to the toold.

> compile for.c > a ssemble box-aut > lin12 100.0. 6002.0 1 ange >locute pourere Embedded system communication mil HOST The Embedded software Hatid The development tools that build built by those tools runs on the the Embedded Software run ona Embedded system general-purpoke computer fig: Embedded system using hout & target machine \* Kerpormance of Hort Machin: -· An application program is developed that runs on hat computer. · It is also called as Development Platform · It is a General purpose computer . It has more capable processor and more memory. . It has different input & output devices. · Capable Operating System. . It containy many developments tools to create output of binary Image . Once a program has been written; compiled, assembled and linked, it is moved to the target platform. \* Pergormance of Target Machine: The cutput of binary image is executed on tauget handware platform · At confinites of two entitles Twiget H/w asuch as processo > Ruthfime environment such as OS . It is needed only for find adjut . It is different from development platform & it doed not contain any development tools. Scanned by CamScanner

5

An each tools can takes one or more files as input and producers a single output file.

This transformation process is performed by software running on a general-purpose computer.

The compiler, assembler, linker, & locator run on a hosp computer.

The Embedded System target platform rons only itself.

These tools combined to produce an executable binary image. "This output of binary image runs on target Embedded sty \* Comá [ing: -· A sophware program that converts source code High level language into low level language. · Compiler translates program written in human readable language into machine language [source code -> Object/file] This object file is binary file that contains set of machine language instructions (opcodes) and data resulting from language transulation process. \* Native compiler. It runs on a computer platform and producers code for that same computer platforme \* Cross compiler: - It suns on a computer platform and produces code for another computer platform. · Compilers can support standard object file formats. Such as COFF [common Object File Format] ELF [Executable and linkable format] etc.. A Member / gnterpreters: -· An assembler is a softwar program that converts source code of assembly language into machine language. · An Interpreter constantly runs & interprets source code as a set of directives. \* linking: - A linker & link editor is a program that takes one or more objects generated by compilers and assemblesss them into a single executable program. The output of the linker is a new object file that contains all of the code and duta from the input object files.

\*Locating: = A locator is the tool that performs the conversion from relocatable program to executable binary image. • The locator assigns physical memory addresses to code and duta sections within the relocatuble program. \* Types of Embedded toolst-· Embedded Hardware took \* Embedded Software tooly · In - circuit & mulator · Edital · Debugger · Assembler ·Simulator & Emulator · compiler · storter kit · Linker · Simulato · Profiler \* Tools processing: [Flow of process] -source code Preprocenso preprocessed codel Compiler Amembly codel Assembles >[object code] Linker 1. braries object code Linker Debugger Scanned by CamScanner

> Embedded Applications:= · Embedded systems used in various applications are listed as Home Appliances: Distiwasher, washing machine, microwave, Top-set box, security system, HVAC syster, answering nt garden sprinkler systems etc. 2. Office Automation: Fax, copy machine, smaxt phone system, 3. Security: Face recognition, Finger recognition, eye recognition modern scanner, Printers. building security system, airport security system, and clarm system optical character 4. Academia: Smart board, Smart room, OCR, calculator, Smart cord EAnglument 1 5: Anstrumentation: Signal generator, signal processor, power Supplier, Procens instrumentation. 6. Telecommunication: Router, hub, cellular phone, IP phone, 7. Automobile : Engine management system, Fuel injection controll anti-locking brake system, air-bag system, GIPS, Cruise Control-8. Entertainment: MP3, Video game, Mind Storm, smait toy. 9. Aerospace: Navigation system, automatic landing system, Flight attitude controller, space explorer, space robotics 10 Industrial automation: Assembly line, data collection system, monitoring systems on pressure, voltage, corrent, temperature, Hazard detecting system, 11. Personal: PDA, iPhone, palmtop i data organizer. 12. Medical : CT Scanner, ECG, EMG, MRI, Glucose monitor, blood prensure, monitor, medical diagnostic device. 13. Banking & Finance: ATM, Smart Vendor machine, cash register, Share market 14- Miscellaneous: Elevators, tread mill, smard card, security ECG: ElectroCandioCriaphy See room etc. EMG: Electro Myolaraphy (muscles detin) MRI: Magnetic Resonance Inaging (body schum)

Scanned by CamScanner

Features of an Embedded System :-

· Embedded systems are called product of Hardware and Software co-derign. Embedded system includes different types of procensols, power supply unit, clock, reset circuit, memories which are considered to be most essential Hardware components of standalone Embedded systems. \* Different types of processors used :-

· Processon: A processon is a heart of the Embedded system It is responsible for execution of instruction and controlling flow of data to and from processor. Différent types of processors available can be categorized

"into four pas board categoriges.

i General Purpose Procensol [GPP]

2- Application Specific System Processo [ASSP]

3. Multiprocessor System and

4- GPP (force & ASIP core [Application specific Induction OUPP!-In may be any one of Microprocensol, Microcontrolley Embedded procenso, Digita Signal Procenso [DSP] 4 Media procenso @ASSP:- It is dedicated for paster processing and useful for applications like real time video processing which in incorporates lots of processing befor transmitting. It may also include some features of RTOS. · ASSP provides Audthardwired solution for most its time consumming tasks.

Multi processor system: As Embedded algorithm has to work with in strict deadline, some times it may not be possible to carry out the same with a ringle processor. . In such a case an ES may go for two or more procensold · Multiprocessons are used when a single processon does n't meet the need of the different tarks that have to be performed concurrently

( GUPP core of ASAP core! -. It is integrated into either a application specific Integrated Circuit [ASIC] 31 a VISI 37 an FPGA core integ integrated with processor units. \* Power Supply unit: -· Crenerally Embedded System has its own power supply whit. · Fourrange of voltage (15.00 +0.250 (2) 3.30 to.30 32.00 +0.20 (2)1.50 +0.20 are used for operation of different Unita. · Additionally 121 + 0.21 supply is needed for a flash of EEPROM and RS232 Serial Interfaces. · Supply of voltage to the chip depends on number of pins provided in the chip which is generally in parti supply and ground. \* <u>clock oscillator</u> The function of this oscillator circuit isto provide a accurate and stable periodic circuit signal to a proceusor The processor need a clock oscillator as clock controls and Various clocking requirements of CPU-(Enternal to the processor) The circuit uses either a crystal or ceramic resonator Stan external Ic attached to the processor. Sinternally associated . The machine cycle includes () fetching code and data from memory and Decoding and execution and (ii) Transperring results to memory The clock controls the time for executing an instruction. . The Crystal resonator gives the highest stability in frequency with temperature and drift in the circuit The internal ceramic generator, if available in a processor, saves the use of the external crysal and gives a reasonable though not very high frequency. . The external IC based clock oscillator has a significantly higher power dissipation compared to the internal processo? ale sonatol.

\* Real time clock of timor units! -

· A timer is suitably configured as system clock sometime Helgerred as RTC (Real Time clock). RTC is used by Scheduler for real time programming. · A hardware timer is a counter that is incremented at a fixed rate when the system clock pulses There are sekeral different types of timens available. A timer/country can perform several different tasks. . More than one timers using the RTC may be needed for various timing and counting need. There may be a hardware and software implementations of timers. · At last one hardware timer device is must in a system which is used as system clock. · A software times is a software that executes and increases or decreases a count variable or an interrupt on a timer output or on a real time dock interrupt. A soptioure timer can also generate interrupt on overflow of count value of the final value of count variable. \* Interrupt Handler :-

· A system possesses a number of devices and the system processol has to control and handle the requirements of devices by running appropriate Interrupt Service Routine (1517) for each. · An interrupt handling mechanism must exist in each system to handle interrupt from various processes in the system. . An interrupt is an event that suspends regular program operation while the verevent is serviced by another program. · Different microcontrollers have different interrupt sources which can include external, timer and serial port interrupts · when an interrupt is received the current operation if Bospended, the interrupt is identified and the controller jumps to an interrupt service routine. There are two sources of interrupt: hardware and software.

·Hardware interrupts include a signal to a pin, timer overflaw and serial port interrupta. Software interrupts are commands given by the programmer.

• There are two different interrupt types: maskable of non-maskable. A maskable interrupt can be disabled of enabled while non-maskable interrupt cannot be disabled and are therefore always enabled.

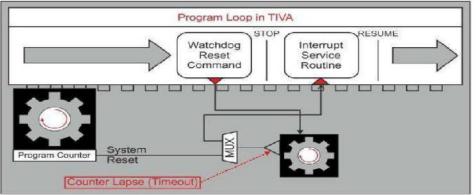

\* Reset circuit and watchdog timer: -

• Reset instruction start execution from starting address otherwise execution start from this address when it is powered powered up. The reset circuit activates for a fixed period and then deactivates to let the program proceed from a default beginning address.

•On deactivation of the reset that succeed the processor activation, a program executes from start-up address. • Reset can be activated either by external reset circuit that activates on power up or by software instruction or by a programmed timer known as watchdog timer.

· Workhog times is a timing device that resets the system after a predefind timeout this time is usually configured and the watchdog times is activated within the first few clock cycles after power up.

• In many embedded systems veret by a watchdog times is very essential because it helps in rescuing the system brom program hangs. On restart program can function normally

Embedded system & makes use of different types of memories based on their features.

I Internal RAM used for registers, temporary data and stack.

I Internal ROM/PROM/EPROM for application program.

I External RAM for temporary data and stack

I Internal RAM for temporary data and stack

I Internal cache available in case of some microprocessored microprocessored.

SEEPTION of plasti memory for saving the results (6) External ROM or PROM for embedding software used in non microcontroller based systems. 7) RAM memory buffers at ports - caches for superscalar ups. · Different types of memory devices in varying sizes are available for use as per requirement. ( Masked ROM or EPROM of blash which stores the embedded software (Rom image). () EPROM or EEPROM is used for testing and derign stages. & EEPROM (5V porm) is used to store the results during the system program. run time. (+) RAM is mostly used in SRAM form in a system. Advanced System uses RAM in the form of a DRAM, SDRAM, & RDRAM. (5) Parameterised distributed RAM is used when I/O devices and subunits require a memory buffer (+ Input/autput units and buses: -• The system gets input from physical devices such as keypods àbairds, sensors, translucer circuits etc. It gets the values by read operations at the port address. • The system has output ports through which it sends output bytes to the real world. It sends the values to output by a write operation at the port address. .In case of some devices a port may be used as both input as well are output port. • There are two types of I/O ports () Parallel port 2 Derial port. · A sevial port facilitates long distance communications and Interconnections. \* DAC/ADC:-· For automatic control and signal processing applications, a system must provide necessary interfacing circuit & sopposere por DAC unit & ADC unit.

•ADAC operation is done with the help of a combination of PWM unit in the microcontroller and External Integrator •ADC operations are needed in systems for voice processing, Instrumentation, Data acquisition system and occutomatic control.

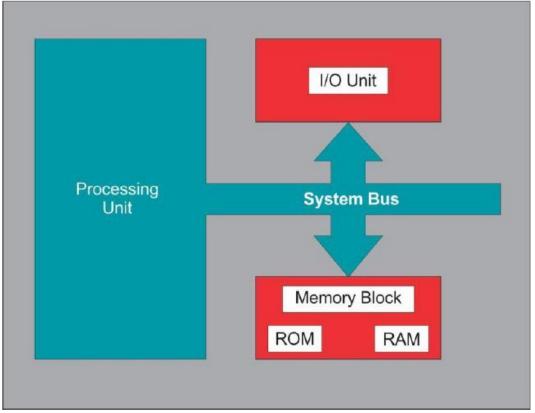

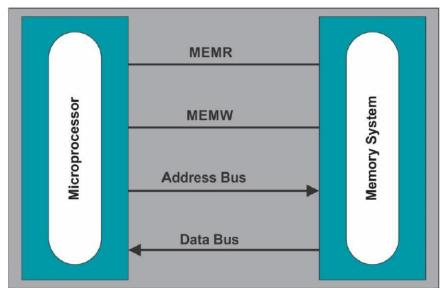

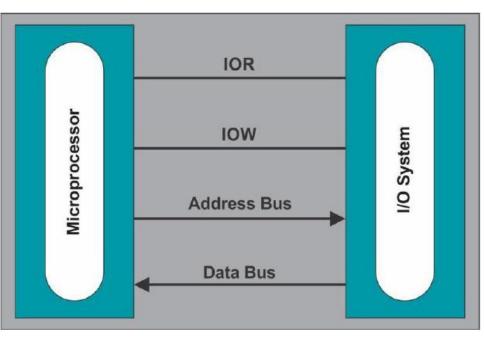

Data and Address Bus concepti-Signals from signals to output doubt Datapath Memory Imput Output Data Join Address Join A typical Bus Structure compaising address, data and control signals.

According to computer architecture, a bus is defined as a system that transfers data between hardware components of a computer 32 between two separate computers.

Initially, buses were made up using electrical wires.

Computer buses can be parallel 82 social and can be connected as multidrop, daisy chain, 82 by switched hubs system bus is a single bus that helps all major components of a computer to communicate with each other.

It is made up of an address bus, data bus and a

control bus.

\* Address burg: -· Address bus is a part of the computer system by that is dedicated for specifying a physical address. · When the computer processor needs to read or write from of to the memory, it users the address bus to specify the physical address of the individual memory block it needs to accens. • When the processor wants to write some data to the memory, it will assert the write signal, set the write address on the address bus and put the data on to the duta burs. · Similwily, when the processor wants to read some data reading in the memory, it will assert the read signa and get the read address on the address but. The size of the memory that can be addressed by the system determiners the width of the oddress but. Ex: if the width of the address bus is 32 bits, the rystem can address 232 memory blocks. · A data bus simply carriers data. Internal buskes carry \* Data bus!information within the processo?, while external bused corry data between the processor and the memory. · Typically, the same data burs is used for both. read write operations, when it is write operation, the processor will put the data on to the data burs. . When it is read operation, the memory controllog will get the data from the specific memory block & put it in to the data bus. +ne procension main that I are in the intermediation between the procensor and other devices with in the computer.

The control burs carriers signales that report the status of various devices Diffectionce between Address bus and deta bus 2-· Data bus is bidirectional, while address bus is unidirational. That means data travels in both directions but the addresses will travel in only one direction to Because address is always specified by the processor. The width of the date bus is determined by the light the individual memory block, while the width of the address bus is determined by the size of the memory that Should be addressed by the system. =) Architecture considerations / Embedded S [ROM , RAM, Timers] !-Functional circuits in a chip or core of Microcontrolly Internal Inputports Procenso Flowh/ 120M control & Internal Inta pres/ External RAP Driken memorius Timense Anterparo Serial JART vatchdog Interropt Communication times controllo port Serial Synchronous Communication Application specific circuits in specific versions FUSM AP Modery PMA circuit-DTMF Controller Circuit CAN Nelworlz Printy Duci-tons Drivers lack controller Controllo Multi- frequency & Interfaces Signaling ch 19: Functional circuit diagram for Embedded System?.

Scanned by CamScanner

· 9+ includers a jetch unit for petching instructions from the memory.

EU-st takecare of every operations of executing an instructions. It consist of Registery st · Exect has circuity that implement the instructions pertouning to data transfor operation and data conversion from one form to another form. · EU Includers the ALU and also the circuits that execute instructions for program. \* Program memory and data memory :memoryers can clustified as two typies. sockey AProxpram memory (2) Date memory. \* Program memory:-· Also called as ARTROM · At to ROM is Nonvolatile memory [Retains its contents when power is removed? . It can't be written & modified at run time + Data memory :-· Also called as RAM · RAM in avolatile memory [consent its contents when power · Duta can be read & written with equal care in removed . It has ability to access any memory cell directly · RAM is much paster than ROM. There is another memory is there i.e cache memory, it is very faster than ream. \* Power Supply circuit --· Power supply is nothing but the supply which is given to the circuit. to provide a accurate and stable periodic circuit signal to the procensol. \* Penet circuil: - In many embedded rystems revet by a watchdog timen, is very essential because it helps in rescuirg the wystern from program hangs.

Scanned by CamScanner

72 \*Timers'-• Timers are generally used to generate Time delays. • At also be made to world as counter. · Timets have many use cases. Such at Creating accorate delays, executing a periodic tark, implementing a PWM ofp & capturing the clapsed time between two events, to vary the speed of data transfer rate i e Baud rate in care 9, serial compose \* Interrupt controller:-· set of special instructions which has to be executed at that perticular point of time. · Managers all the interribpt requests on a priduity basic and provide. individual interrupt service by cpu. \* Input and output Ports:-· Port is nothing but an external pin which is used to interface à dévice to this processor. \* Served communication: - iscunsfer data bit by bit. \* Interfactory. \* Pascillel communication: Transfer bull of data. \* Driver Circuit: Which is use to controll other Circuits >Embedded Processols and their types:> · Processor is the heart of an embedded system. It is the basic unit that takes inputs and produces anoutry after processing the data. · For an embedded system d'erigner, it is necessary to Have the knowledge of both microproceusors & river controls · A procensors has two "ensential writes. · Rogram Flow control writ((U)/BIU · Execution Unit [EU]

· control unit: This unit in processors performed the program flaw control operation invide an Embeted System. The control unitalso acts as a petching unit for petching the set of instructions stored inside a monorg. · Execution unit: - This unit is used for execution the Various tailes invide a processors. It mainly comprises of withmetic and logical unit (ALU) and it also include a circuit that executes the instruction sets used to perform program control operation invide the procensors. · Procensons invide an embedded system are of the following categoriet. D'General purpose processor - (GIPP]:-·GIPP is used for proceeding signal from input to output by controlling the operation of the system bus, address but and date bus invide an Embedded system. • GPP with instruction set designed not specific to the applications. - Microprocenso? - Embedded procensol \*(2) Application specific gnatruction set processor (ASIP]:-· An ASIP is a processor with an instruction set designed for specific applications on a VLSI chip. · ASIP in application dependent instruction processors. - At is used for processing the various instruction set invide a combinational circuit of a an Embedded System. - Microcontroller - Embadded controll microcontroller - Digital signal Procensor (DSP) & - média processo?. Application specific Septem Procensor [ASSP]:for proceeding right of Embedded system. Therefore

for different application performing tank a unique set of system procensols is required. \* @ single purpose processous EPP]-. This type of processor is designed to execute exactly on e program. An embedded designer creates a single purpore processor by designing a custom digital circuit. · SPP une used for specific applications or computations 87 as controllers 152 peripherals, direct memory accesses and buset. · SPP used in Embedded systems include: 1. Coprecensol [ Ex: Floating point procerning]. 2. Craphics processol: An image consists of a number of pixels-3. Pixel coprocernol: High-resolution pictures follmats. 4-Encrption engine: À suitable algorithm runs in this processor to encrypt data for secure transmission. 5. Decription engine: A suitable algorithm runs in this procensor to encrypt data for secure decrypt the. encrypted duta at receivents and. 6. DCT9/ DCIT = [A discret coun transformation & invers transformation] processol: is required in speech & video processing. 7. Protocol stack procensor: which has a number of header Golds, in prepared before an application data is sent to network. 8. Network processol: Functions are to establish a Connection, finish, send & receive acknowledgements, send and receive bretransmission requests and check and correct received duta prame errors. 9. CODEC [coden 2. Decoden]: - in a processor circuit that encoders input an decoders the encoded information or bits or rignals into a complete set of bits or original signal.

\*(5): GPP core of ASIP core:-

"CIPP core & ASIP core is integrated into either an ASIC. [Application specific Integrated circuit] & a VISI or an FPGA cove integrated with processor units. • For a number of applications app cove may not be a suitable solution. · For various security application, smart cord, video game, mobile Internet, Orbps transverver, Copps LAN, minsile system needs a special processing unit on a VLSI design circuit to junction as a procensor. · These units are called Application Specific Anstruction Processon Somtime for an application both configurable processon ( FPGA or ASIP) and non-configurable processon (DSP &T HP & MC) might be needed on a chip ! Generally this type of applications are vary important in some killer applications such as HDIV, cell-phone etc. [applications which in uneful to millions of people?. \* Multicore procensation at multiprocensation · As embedded algosittom how to work within strict deadline, sometimers it may not be parrible to carry out the same with a ringle processor. An such a care an embedded system may go for two or more processors. similar requirement may be needed in moder cell phones which has to perform number of tarks. · Multiprocensors are med when a ningle procensor doesn't meet the need of the different tarks that have to be performed concurrently The operations of all processors are upnchronized to obtain an optimum performance. A Microprocenso? - LIP is a programmable digital device which here high computational capability to run anomber of applications in general purpose repternt.

# # gt does not have memory of I/o ports built within its architecture. So, these devices need to be added externally to make a system functional. · In embedded systems, the design is constrained with limited memory and Ilo peatures, so microprocensorsare uned where system capability needs to be expanded by adding external memory and I/0" \* Microcontroller! -• A 40 has a specific amount of program and data memory, as well as Ilo ports built within the architecture along with the cpu core, making it a complete regitem. > As a result, mort embedded mystems are microcontrolley based, where are used to sun one or limited no of applications \* Embedded Procensol'-· Embedded processors are specifically drigrod for embedded systems to meet design constraints. They have the potential to hundle multituling applications. The performance and power efficiency requirements of embedded systems are satisfied by the use of embedded p # DSP: DSP are uned foil rignal procensing applications. such as voice or video comprension, data acquinition, Emage processing or noise and echo concelleition. A ASIC: ASIC is banacelly a proprietary device derighted and used by a company for a specific line of products. It is specifically an algorithm called intellectual property core implemented on a chip. \* FPGA: FPGA have programmable macro cells and their interconnects are configured based on the derigen. They are used in embedded systems when it is required to entance.

· Commonly used microcontrollers in small-, mediumand large-scale embedded systems. Small Scale Embedded System 8/16 bit Hicrocontrolly 68HCILXY 8051 family PIC. 6F8X Hitachita Medium Sale Embedded System 16-bit Microcontrolles 6BHC1ZXX, 6B+K16XY Hitachi D64F2623FA (BOSIMX) [PIC 16F876, PICPS Large Scale Embedded system 32-bit Microcontrolo Hitchi St1704ST ARM family costed-13, Atmet AT91 serves, CI6X (STIO Series, Philips LPC 2000 Series, Texas Instrument, TITASLIFORIBIM, Sorngung 53C4 4BOX

\$ #Memory Types . Remory in the mont essential element of a system because without it system can't perform simple tasks. The semiconductor memory can be classified into two types. (1) Volatile Memory D Non-volatile Mernory \* Volutile memory!--> RAM - Static RAM - Defnamic RAM \* Non-Volatile memory: --> ROM - Masked ROM - OTPROM | PROM - EPROM - EEPROM - FLASH -> NNRAM (Battery Backup RAM) \* RAM (Random Access Memory):-. It is also called as "reade write memory" or the main memory or the primary memory. • The programs and dute that the CPU requires during execution of a program are stored in this memory. . It is a volatile memory as the data loses when the paver • At has ability to access any memory cell directly. • Volatile memory is used for data, and small microcontroller • Often have very little ream. RAM is much fautor than ROM · RAMI is forther classified into two types. - Strar [ Static izandom Accens Memory ] - DRAM & Dynamic Random Access Memory 7. SRAN:-. The SRAM are memories that consist of circuits capable of retaining the stored information as long all the power is applied.

That means this type of memory requires constant part · SAAM memoriles are used to build cache memory. · A single cell of stran needs six transiders. Tran therefore takes up a large of silicon, which makes it expensive · DRAM storers the binary information in the form of electric \* Dy ramic RAMcharges that applied to capacitors. . The stored information on the capacitors tend to lose over a period of time and thus the capacitors must be periodically recharged to retain their usage. The main memory is generally made up of DRAM chip This needs only one transistor per cell but must be represhed regularly to maintain its contents, so it is not used in small microcontrollers. word 2inp write Tead outro BitLino gig: Single cell DRAM. att fig: KSIZAM porced Single Cell • There are mainly 5 types of DRAM: \*. I. ADRAM [Asynchronous DRAM]: • The DRAM described above is the asynchronous type DRAM. The timing of memory device is controlled asynchronously. · A specialized memory controller circuit generated the necessary control signals to control the timing. \* 2. SDRAM Synchronous DRAM]:-• There RAM chips access speed is directly synchronized with the CPU's clock, For this, the memory chips remain ready for operation when the CPU expects them to be ready.

\$ . These memories operate at the cpu-memory bus without imporing wait slates. · SDRAM is commercially available as modules incorporating multiple SDRAM chips and forming the required capacity for the modules. \*3 DD RSDRAM [Double-Data-Rate SDIZAM]: • This paster version of spiram performs its operations on both edges of the clock signal; whereas a standard SDIRAM performs ets operations on the rising edge of the clock signed "" they transper data on both edges of the clock, the dete transfor rate is doubled. To access the data at high rate, the memory cells are organized into two groups. Each group is accessed separately. • The RDRAM providers a very high data transfer raite \* (4) RDRAM [Rambus DRAM] over a narrow CPU memory bus. · At ones various speedup mechanisms, like synchronous memory interface, caching inside the DRAM chips and very fant signal timing o the Reimburs deter bus width is 8 or 9 bits. 3 cDRAM cache DRAM O SRAM has lower access time, B DRAM has higher access fime, so it is fanter compared to DRAM So it is slower than SRAM. DRAM is contien than DRAM DRAM controllers than SRAM B) STRATT requires constant power B.) DRAM offers reduced power Supply, which means this type consumption, due to the fact that of memory consumers more power the information is stored in the capacity a Due to complex internal circuiting Due to the small internal less storage capacity is available circuitry in the one-bit memory compared to the same physical cell of DRAM, the large storage copacity is available size of DRAM memory chip. (5) DRAM has high packaging 3) SRAM has low packaging density. density.

Scanned by CamScanner

\* ROM [Read Only Memory]:-· It is not volatile memory. Always retains its data. · Used in embedded systems or where the programming needs no change. • It is used as program Memory in Microcontroller. • It can't be written or modified at run time. There are many types of nonvolatile memory • The data are encoded into one of the marks used for photoli-theopaphy and written into the Ic during manufacture. • This memory really. I work and all of the the \* Masked ROM!-• This memory really is read-only. It is used for the high-volume production of stabe products , because any changes to the tabe modeling. Change to the data requires a new mark to be produced at great expense. \* OTPROM (One-Thme Programmable ROM):-. This is just PROM in a normal package without a window, which means that it cannot be exaded. It can be programmed one time only. Used when the firmware is stable and the product is shipping in bulk to costoments. · Devices with OTPROM are still widely used and the first family of the MSP430 used this technology. \* EPROM [Erazable Programmable ROM]:-As its name implies, it can be programmed electrically but not erared. Device munt be exposed to ultraviolet(W) light for about tento twenty minutes to couse them. . We can exare the contents of the chip and rewrite it with new contents, typically several thousand timer. [uvlight expored, can errore all the previous data] \* EEPROM'S Can be programmed and eraved in-Circuitie. without remaining from hardware kit, by applying • The contents of this memory may be changed during run tim (similar to RAM), but remains permanently saved even if the power supply is off (similar to ROM.)

| • FFPRO   | Mr are          | also limite                                                | d to H  | he numbe              | 7 of cras   | e-wr                |

|-----------|-----------------|------------------------------------------------------------|---------|-----------------------|-------------|---------------------|

| that (a)  | he De           | erformed (e.g                                              | ,100,00 | 0) but sup            | port updat  | es (co              |

| (Noted)   | to ind          | ividual byte                                               | J. When | eas epr               | 0.P1 149    |                     |

| TIACI     | Memore          | the off                                                    |         | 1                     | alactricc   | ullu &              |

| FLASH     | in he t         | the most com<br>the most com<br>is designed<br>of large cr | med an  | ld eraned             |             | and a               |

| lin now t | by far          | the most corr                                              | mon ty  | pe of me              | morg.       | onati               |

| . Elanh   | Memory          | is devictured                                              | 1 107 h | igh speed             | . & high a  |                     |

| at the    | expense         | of large cr                                                | are blo | cks.                  | Nor of F    | EPRO                |

| - The a   | 1-0.1           | Litterance O                                               | that is | ndividual             | byles I     |                     |

| can be    | crased          | but FLASH                                                  | can be  | crased                | only in bl  | OCKA.               |

| Microc    | mtraller        | is use NORF                                                | ZASH, u | shich is              | slaver to   | write               |

|           | of the maintain |                                                            | S. NAND | FLASH PA              | used in bu  | IK                  |

| but per   | mil's 30        | indom access                                               |         | used only             | a sprially  | inva                |

| Storage   | device          | s and can t                                                |         | anove L               | (Det)-      | Ī                   |

| Acharact  | eristics        | of the val                                                 | ious in |                       |             |                     |

| THERE     | Volatiles       | Writeable?                                                 | Erase   | Max Erche             | Cont/129    | spee                |

| gree      |                 |                                                            | Sig     | <u> </u>              | - Der Cilo  | Fax                 |

| SRAM      | Yes             | Neeves                                                     | Byte    | unlimited             |             |                     |

|           |                 | yes                                                        | Byte    | Unlimited             | Moderate    | Mode                |

| DRAM      | Yes             | [0,                                                        |         |                       | Anexpensive | Fart                |

| Marked    | NO              | 021                                                        | nja     | nla                   |             |                     |

| Ron       | 140             | once, with a                                               | 1       | n ja                  | Moderate    | Fad                 |

| RRAM      | NO              | device                                                     | nla     |                       |             |                     |

| PROM      |                 | Programmer                                                 | Entire  | Limited               | Moderate    | Fart                |

| EPROM     | NO              | yes, with a                                                | Chip    | [consult<br>dutuched] | 1 We want   |                     |

|           |                 | Produce                                                    |         | Limited               |             | Fart-for            |

| EEPROM    | NO              | Yes                                                        | Byte    | (consult<br>datashet) | Expensive   | sav.                |

| ••        |                 |                                                            |         | limited               |             | excreption          |

| Flash     | NO              | yes                                                        | Sec-107 | [consult<br>datester] | Moderate    | Faut to 2<br>Skars- |

|           | 67.             |                                                            |         | Occurred J            | 6           | excue fur           |

|           | 67.             | ,                                                          |         |                       | mi manisim  |                     |

| NUTRAM    | NO              | Yes                                                        | Byte    | untimited             | STATLY.     | Fart                |

.

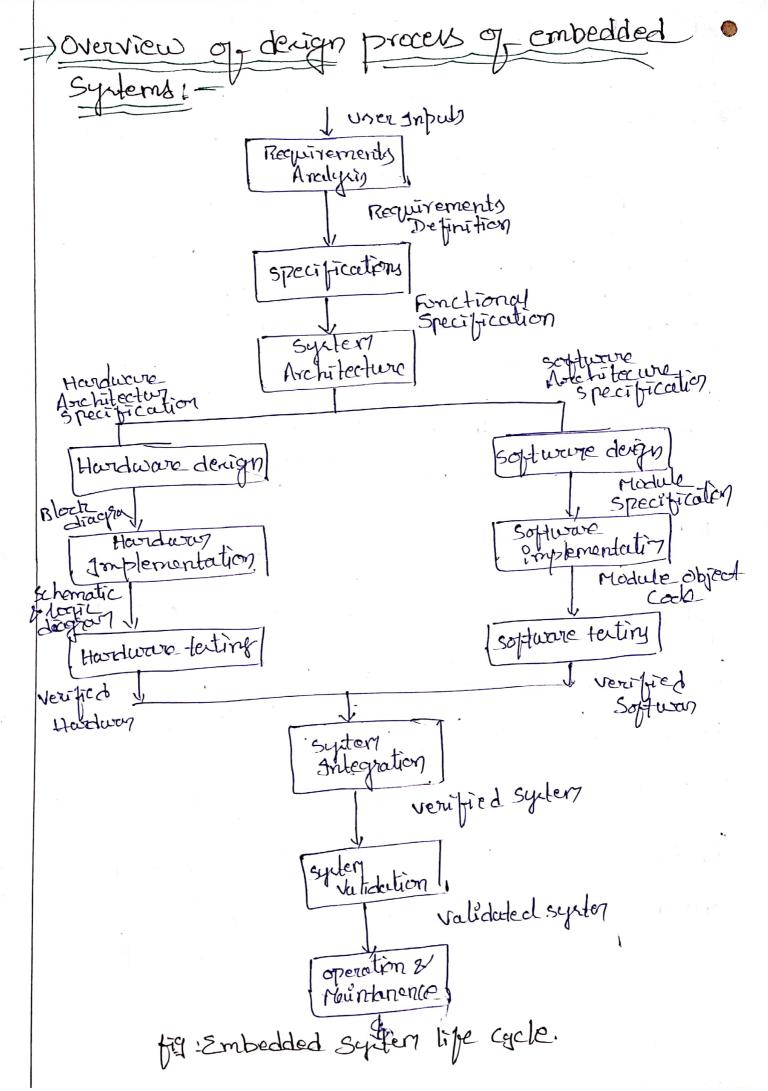

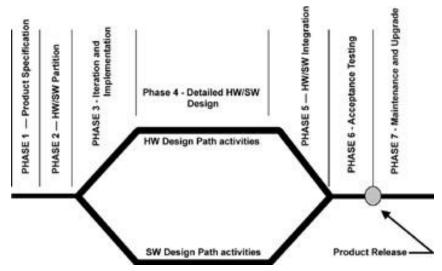

• The important spoteps in developing an embedded syder are. Requirements 1. Requirements Bottomyp TUP-down 2 - Specifications derign Specification gerign 3- Architecture (Architecture) 4- Components 5 - System Integration (components) (system Integration fig= major levels of abstration in the Using it, derigen process. · There is two kind of methodologys 1- Top-down deright methodologig [ z-Bottom-up derign methodology Esteps are shown in the 129 and a arred - line arrows \* Top-down derign: Begin with the most abstract description of the system and conclude with concrete details \* Bottom - up derign: Start with components to build a ryrtem, Ending up with perticular requirements. · Mont of the people prefor bottom-up approved enigh because we do not have purject insight into how later stages of the design process will turn out. \* Major goals of the derign to be considered : · manuflicturing cont · Performance (both overall speed and deadlines) · Paver consumption. \* Tankswhich needs to be performed at each step: . We must analyze the design at each step to determine how we can meet the specifications. · We munt refine the derign to add detail. · We must verify the daugh to ensure that it still meets all system goals, such as cont, speed, & so on..

1) Requirements:-· Antormal description gathered from customers is Known as "requirements" · Requirements can be of two types -Functional requirements · It need output as a function ofginpat - Non-gunctional requirementa. · Some of the non-functional requirements •In the requirement stage power can be specified in terms og battery lipe. · However, the allowable wattage can't be defined by the \* Physical Size Eweight: · Depending on the application, the physical sizes weight of the final system can vary a lot. · If the application involves a handheld device then there ure constraints on both the size & weight of the device. . However, if it is an industrial control system then there is no constraints on the size & weight. The cont and usability of the system are effected by its + Feijormancetspeed. The performance metrics can be combination of soft metrics and Hard metrics. The system's purchase price or the target cont is very important. complete cont or simply cont includes the \* cont:-· Manufacturing cost : it is the cost of assembling and following two components · NRE contro [Non-Recurring Engineering]:- NRE contro are the cost of hiring personal and other design related contro.

Ľ \* Requirements form or Requirements chart:-• The requirement form/chart acts like a check list when the project is in limitial stagers. EZ: - A sample form is given below Name.'s Purpose: what the updem supposed to do An puts: autruts: Functions: functionality of the hypter Performance: manufactoring cont: Power: Physical size & weight: Fq: Sample requirements form. · Name: - Naming not only describe the purpose of the machin but also Fielpful while commiting about the project. · Purpore: This should be a brief one of two line description of what the system is supposed to do. · Inputs and outputs: This field requires information about type of Ilo devicero, Data characterintics & types of data. · Functions: - A detailed description about the functionality of the machine is described in this field. · Performance: An order to assume proper functionality, Performance requirements should be identified before hand and they mont be measured carefully. · Physical size & weight' In order to take architectural decisions the approximate physical size and weight of the system is · Power: The rough idea about power consumption can very helpful. Decision about whether the system is buttery based & non-battery is important here. Example: consider an example of a cips moving map system sample requirement chart. Name: GPS Moning map purpose: consumer-grade moving map for driving use

Scanned by CamScanner

Inputs: & control buttons and Paver buttons 0 outputs: Back-list LCD display with 400x600 pixels Functions: User 5-seceiver GIPS system, 3 user-seletable resolutions & displays current bongituder lattitude. Performance: updates screen within 0.25 seconds upon movement. Manufacturing cont: RS 2000 100 mw Physical Bize & weight: Not more than 2"x 6" & 12 ounces! Power: (2) Speci (reation!. · Specification servers as the contract between the custometrs and the system architects. · Specification is essential to create working systems with a minimum of derigner effort. . It must be specific, understandable and accusately reflect the curstomerily requirements. Example's considering the example of the GPS system, the specification would include details for several components. - Data receiver from the CIPS Batfellite constellation · Map data · User interface · operations that must be performed to satisfy Customer · Back ground actions. · Drifferences blu Requirements & Specifications: Specifications Requirements () An informal description gar- Or A contract between customers Enrequirement form is used to 2 UML is used to give clear & give a formal listing of requirement proper specifications. 3) The banic needs to derigna 3) The description of project is system are given by system given by system specifications requirements

v ( ) More complex schalling tails (4) Levis challenging Tarl 0 (5) Requirements need not be Specifications should be perfect Perfect enough in order to develop correct application. DGood prycological skills are 6) croad Engineering skills are stequired to produce good syster redrived to brodrice docc requirements specifications. 3) Architecture Derign:-. The specification describes only the functions of the system; Implementation of the system is described by the Architecture. • The architecture is a plan for the overall structure of the system . It will be used later to derign the components. Excemple! · A banic block diagram of the GIPS system shows the major operations and the data flow among the blocks Display search GPS Renderer receiver engine User interface zuta pene fig: CIPS system data flow and operations. • This block diagram is an initial architecture that is not based either on hardware of on software but combination of both. • This block diagram explains about crips navigating system where GIPS succeiver gets corrent ponition and the destination is taken from user, digital map for source to destination is found from detabase and displayed by the renderer. The system block diagram may be refined into two block diagrams - hardware and software. • The refinement of Hardware and software architecture should begin only after the initial architecture is designed.

CPU Frame Data bore W/per ponderey search. Display Memory (positions) Interforme timer tig: crips system Hardware 1 fig: GIPS system Software. · Handware containts of one central cpu sorrounded by memory and I/o devices. · We have chosen to use two memories that is frame buffer holds the pixels to be displayed and memory for program (d) data which will be used by CPU. · A Bus is used to connect all these components • The soptware block diagram is some as initial architecture but an additional timer is added. This timer is to control when we read the buttons on the user interface and render · Finally the Architectural descriptions must be designed to - Satisfy user requirements [Functional & non-functional] - Include all the required functions. - Should meet speed, cont, Power Discuirements - meet all the specifications 4) Derigning Hurdware and software components:-The architectural description tells us what components we real • The component design effort builds those components in conformance to the architecture and specification. . The components will be in general includes both Hardware and software modules. Some of the components will be ready-made (example", CPU, memory chips) · Some of the components must be designed by user's also which nechive lot of custom programs.

(5) System Integration: → . The system integration deals with the integration of avsembly of the components created. . We know that Hardware and software made seperatly and people who are working with Hardware software ty they made it perfectly worked out well. But when we are integration these things with simulator, simulator does not read the real time problems so that Bugs are typically "However, good planning, phase level development, good found during system integration. tests running at each phase can assid in finding bugsquizity · By debugging few simple bugs carly, more complex of · System integration is difficult because it usually uncover The debugging facilities for Embedded Systems are usually much more limited than the desktop systems. · Careful attention to inserting appropriate debugging to facilitiers during derign can help ease system integration pooblems. Programming languages and tools for Embedded \* Programming languages:-· code is typically written in court, but various high-level programming languages, such as python and Java script, are now also in common use to target microcontrollers and embedded systems. Ada is used in some military and aviation prejected. \* Machine code!-. The binary data that the processor itself understands. · Each instruction has a binary value called an opcode. · At is unrecognizable to humans, unless you spent avery long time on low-level debugging.

\* Ansembly language: · Little more than machine code translated into English. · The instructions are written as words called memonics · It does a little more than direct translation, but not a bit, rather than binary Values. nothing like a compiler for a high-level language. · A mayor disadvantage of assembly language is that it is intimately fied to a processor and is there fore different for · Mont programming of small microcontrollers was done in civisembly language. • The most common choice for small microcontrollers nowcidays. • A compiler translates c into machine cade that the CPU can . This brings all the power of a high-level kinguage - data procens structures, ponctions, type checking and so on, but a can usually be compiled into efficient code. · Compilation used to go through assembly language but this is now less common and the compiler produces machine code directly. #ctt:-· An object-oriented language that is widely used for langer devices. A restricted set can be used for small microrontrollers bus some features of ct+ are notorious for producing highly inefficient code. · Embedded C++ is a subset of the language intended for embedded systems. . Java is another object-oriented language, but it is interpreted rather than compiled and needs a much more powerful processor. · Available for a new processors. The usual BASIC language is extended with special instructions to drive the peripherat A BASIC:-This encibles programs to be developed very rapidly, without detailed understanding of the peripherals.

. Disadvantages are that the code often runs very slowly and the hardware is expensive if it includes an interpreter. \* Krogsamming Tools: -\* Editol: - At enables users to write codes for high level as well as assembly language is computer. · Different peatures like addition, deletion, copy, in sertion At saves the content in a faile with user defined or default are made available for easy writing. extension. User can make necessary modification of saved. files as and when required. \* compiler: - It takes the input of whole high level source code and converts it to machine readable object code. .It may include fonctions, library soutines etc- for \* Interpreter: - at converts high-level codes to machine reado recidable poim line by line. Like compiler it may also include functions, library routines etc. for conversion. \* Ansembler: It is used for conversion of assembly language programs to executable breazy files. . It creates the list file which has address, source code and heradecimal object codes. It is procensor specific. \* GOAS assembler: Goas assembler assembles the assembly code of target processor as assembly code of the processor of the PC used in the system development. Later it provides the object codes for the target processor. These will be the final coders used for the developed system. simulated; It is the program which can simulate all the functions of an embedded system circuit including additional memory and perepherals. At is independent of a particular target gystem. \* stethoscope: This program is used to keep track of dynamic change in program variables and parameters. It can

demonstrate the sequences of multiple processes, tanks, threads that execute and keeps entire time hintoly Trace Scope: At traces the change in module according to time. Accordingly list of actions to be initiated at derived time is also prépared. \* IDE (Integrated Development Environment: Total software and hardware environment consist of simulator, compiler, consembler, crons ansembler, logic analyser EPROM/EBPROM, application codes, burners defines the integrated development environment of the system. \* Locator: Locador program uses cross-assembler output and a memory allocation map and provides locator program aufat \* characteristics of a programming language:-· A programming language munt be simple, easy to learn and use, have good readcibility & human recognizable. · Abstraction is a moment-have characteristics for a programming language in which ability to define the complex structure and then its degree of usability comes. · A portable programming language is always preferred. · Programming languages efficiency munt be high so that it can be eavily converted into a machine code and executed consumes little space in memory. · A programming language should be well structured and documented so that it is suitable for application development · Necessary tools for development, debugging, testing, maintenence of a program must be provided by a programming language. . A programming language must be consistent in terms of should provide single environment known as IDE.

# EMBEDDED SYSTEM UNIT-II Embedded Processo Architecture

UNT Embedded Processor Architecture => CISC VS RISC design philosophy:-The architecture of the CPU operates the capacity to function prom "Indruction set wichitecturate" to where it was derigned. · Instruction set can be defined as the communication interface between the processor and the programment. · Every procensor has its own indruction set implemented in the hardware to execute instructions. · Programmers can either one any language to write the program - Accordingly, a compiler or ansemblez can be used to translate the program into machine under--standable language following the processor instructionso · There are two architectures of indiraction set implementa () RISC [Reduced Instruction Set computer? (2) CISC [Complex Anatruction Bet computer]! · A reduced instruction set computer is a computer which only uses simple commands that can be divided into several int ructions which achieve low-level operation within a single all cycle, os its n[1] is designed to reduce the Execution time by smplifying the instruction set computer] \* CISC: · A complex instruction set computer is a computer where single instructions can perform numerous low-level operations like a load from memory, an arithmetic operation, and a memory store or are accomplished by multi-step processes or addressing modes in single instructions; as its name proposes [1]+ is designed to minimize the number of instruction program Differences between RISC & CISC:->

TRISC Stands for Reduced Instru-O CISC Stands for complex ction Set computer. Instruction set computer

| and in                     | RISC                                    | <u>CISC</u>                                                    |

|----------------------------|-----------------------------------------|----------------------------------------------------------------|

|                            | ERISC processors have simple            | E) CSIC processor has complex                                  |

|                            | instructions taking about one           | instructions that take up multiple                             |

|                            | clock cycle. The average clock          | clocks for execution. The average                              |

|                            | cycle per instruction is 1.5            | clock cycle per instruction is in                              |

|                            |                                         | the range of 2815.                                             |

| 1                          | 3 Performance is optimized              | 3) Perpormance is optimized                                    |

|                            | with more focus on software             | with more focus on Hardware.                                   |

|                            | (4) gt has no memory unit &             | Wat has a memory whit to                                       |

| 10.1                       | Uses a separate Hardware to             | implement complex instructions                                 |

|                            | implement intructions.                  |                                                                |

| 6.                         | 5) It has a hardwired unit of           | 5) It has a microprogramming                                   |

|                            | polyouroung                             | runit-                                                         |

|                            | 6 The instruction set is reduced        | 6 The instruction set has a                                    |

| 1                          | inc it has only a pew instruction       | 6 The instruction set has a<br>variety of different intruction |

|                            |                                         | that can be used for complex                                   |

| 13                         | The sector of the sector of             | operations.                                                    |

|                            | Primitive.<br>Demplex Addressing modes  | DCISC already enports                                          |

|                            | are synthesized using the software      | Compley Addressing moder                                       |

| (                          | 8) Multiple register sets are sta       | 8) Only tras a similar receiver got                            |

| ).                         | 8) Multiple register sets are press     | poind has a single offision of                                 |

|                            | 9 RISC processols are highly            | They are normally not pipe                                     |

|                            | pipelined                               | -timed or less pipelined                                       |

| 1                          |                                         | () The complexity lies in the                                  |

|                            | with the compiler that executes         | D the complexity lies in the microprogram.                     |

|                            | Has proceed to                          |                                                                |

|                            | the program                             | (1) Execution time is very high.                               |

|                            | 14) Execution time is very less.        | (12) code expansion is not                                     |

|                            | Trode expansion con be a                |                                                                |

|                            |                                         | Problem                                                        |

|                            | 3 Decoding of instructions is           | 13 Decoding of instructions is<br>complex.                     |

| la                         | Simple                                  | complet.                                                       |

| 1                          | in It does not require extern           | (in) gt requires external                                      |

|                            | memory for calculations                 | memory for caladi                                              |

| n på so<br>Star<br>Star st | (15) RISC Architecture is used          | 15) CISC Architecture is used                                  |

|                            | in high end applications                | in low-end applications.                                       |

| đ                          | · 전문· · · · · · · · · · · · · · · · · · |                                                                |

1

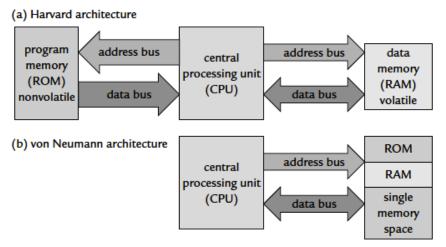

such as vide processing, such as security system, home relecommunication and image automation, etc., processing. # Won FNeamann Vs Harvard aschitectore -> Architecture Architectoron Hardwired Data Antractions control unit K control unit path Data path Instruction Microprogram Data cache / Cache cache control unit ALC PROPERTY Instruction Mort in the Merry Mainmemory + Data 111 Mainmemory 1 64 have the state of a size of said day that Non-Neuronan Vs Harvard Architecture; · Every cpu requirers man and ROM, The arrangement of TRAMBOR ROM/ Data & program memory with respect to CPU that is known as the Architecture of the Amicrocontrollo and there are two tectiniques the CPU can connected to the data and program memory. (). Harvard Architecture (2) Von Neumann Architecture Harvard Achitecture / Non-Neumann Architecture ALST P.J. 1 Data rogram. CPU ABUS AB ROM methory t memory A-BOS CPU (RAM) (ROM) RAM nonvolatile PB D-BUA volafic Single D-BUS AB -) Addreas BUS space DB-J Dada BUS W9t has seperate data and (1) It has common data and program memory. program memory.

Scanned by CamScanner

(2) At requires more hardware, DAt requires lens hardware Because seperate data and because as requires only one address bas for each memory. data and address bud 3) It Requires less space B) + Requires more space @ Only either data or individing Di Processor can betch duta and instruction simultaneously. can be betch at a time 5) speed of Execution is she 5 speed of execution is fart 6) Empty space in program 6) Memory size for data and Instruction can be adjented memory cannot be used for or interchange data 37 vic versa 7) control whit or controlling 7) controlling or control unit Rs simple as compared to is complex, since date and instruction are jetch simul- Hasvard Architecture, Because Single Address & Date Bus taniously 1900 petch date & Inchroction. 18 2-set of clock cycles require 8) single set of clock cycle · cycle por data jetch » Sufficient of this part Leycle for intraction jeth M (K) PY 9) Ripelling is powible (D pipelling is not powerble 1) program contents can be D. Difficult for program early modified by itself contents to be modified by the program itself in widely used in MicroController (1) widely used in Microprocesso 12) Eq: Antel 8051, PIC, ARM9et (2) Intel 8086, MSP430, ARM7 etc. Mass John Jan A 也同时一种收 · 医中门酸的小小的(例) 网络圣卢兰之间 开销 は ap. の人物の内容は かったが 生きり COMPANYA, CREAT PRIM  $\frac{\partial \Omega_{i}}{\partial t} = \frac{\partial \Omega_{i}}$

=> Introduction to ARM architecture and Cortex - M series: The patron of the time studies · The ARM-cortex microcontroller is a mont popular microcontroller in the digital embedded system world · It convints of enormous features to implement products with an advanced appearance . The ARM stands 107 "Advanced RUSIC machine" and it is 32-bit reduced indruction set computer micro 11 14 14 controllo7. · It was first introduced by the "Acron computery organization in 1987. April Moulde have Beneffits to Embedded system Features Olligh Performance Ensure the system has a fast response Dias power consum-Makes the system more energy ption. 3) Low Silicon area reducers the size and also consumes leas joures. "High code dennity Helps combedded system to have less starob di memory, pootpoint. d/store used to load data from the memory architecture to the ARM CPU register or store data from 5) toud store the cpu religion to the memory. enables the memory access when required (6) Register bank with Required to perform most on the operations within the CPU and provide largenomber of working reginers paster context switch in a multiterking Application. bellined the working H. John of holdy. The ARM microcontroller architecture come with a pew different respions and each one has its own advantage and disadvantager.

Scanned by CamScanner

\* ARM7: has three-stage (petch decode, execute) pipetine of Von-Neumann architecture where both address and data use the same but. It executes ust instruction set. To stands for Thumb. \* ARM9: has five-stage Eletch decode, execute, memory write] pipeline with high pergormance, Harrourd anchitecture with seperate instruction and dota bus. ARMY executions vAT& v5TE instructions gets, Estands for enhanced indructions. \* ARMIO'- has siz-itage (getch, insue, decode, execute, memory i write) pipeline with optional vector floating point unit and delivers high floating point performance. ARMIO executes VSTE instruction setA. \*ARMIL: their eight-stage pipetine, high performance and power efficiency and it executes v6 instruction But. with the addition of vector ploating point unit, it perfor ms part floating point operations. • The ARM cortex microcontroller is a advanced microcontroller in the ARM pamily, which is developed by the ARMY7 curchitecture. \* A Basic architecture of the ARMY7:-[Block diagram shown in next page • The Register Bank has sizteen general purpose registers (RO-BIS) and a CPSR [current Program statu's Register] which are accessible by user applications . In addition to that, it has twenty numbers of, banked siegisters specifically used for different operations modesof ARM core . These are invisible to user applications. • The register bank has two read ports to read operand! and operanda and one write port to write back the resout

Address BUS A [31:0] control 1 Address Register SI TAN MAN XYY WS M Address 1. 1. 1. 1 Incrementer Instruction (PC Register Bank A THUS decoder 16 (Rot Rig), LPSR, 9 Min y control MACK 10gic PSI D. COST W C Barrel Shiffer 138361 ALU DITIN Dutce integinter registy Data crit Or ID DIVITAT ON 581.10 Dat BUS D [31:0] and the opening Fig= ARMI Architecture. result of operation to the any register specified in the instruction. . It has an additional bidirectional port to update the program counter with address register and incrementer! Address register content is incremented at every sequential byte access by the incrementer but the program counter is incremented by four in ARM statindruction set of the core or is incremented by 2 in Thomb introction set of the core at every instruction access. · Address sequences by connected to the address bus. . The barrel shifter can shift or rotate operand 2 by speci--fied number of bits prior to conthinetic or logic operations.

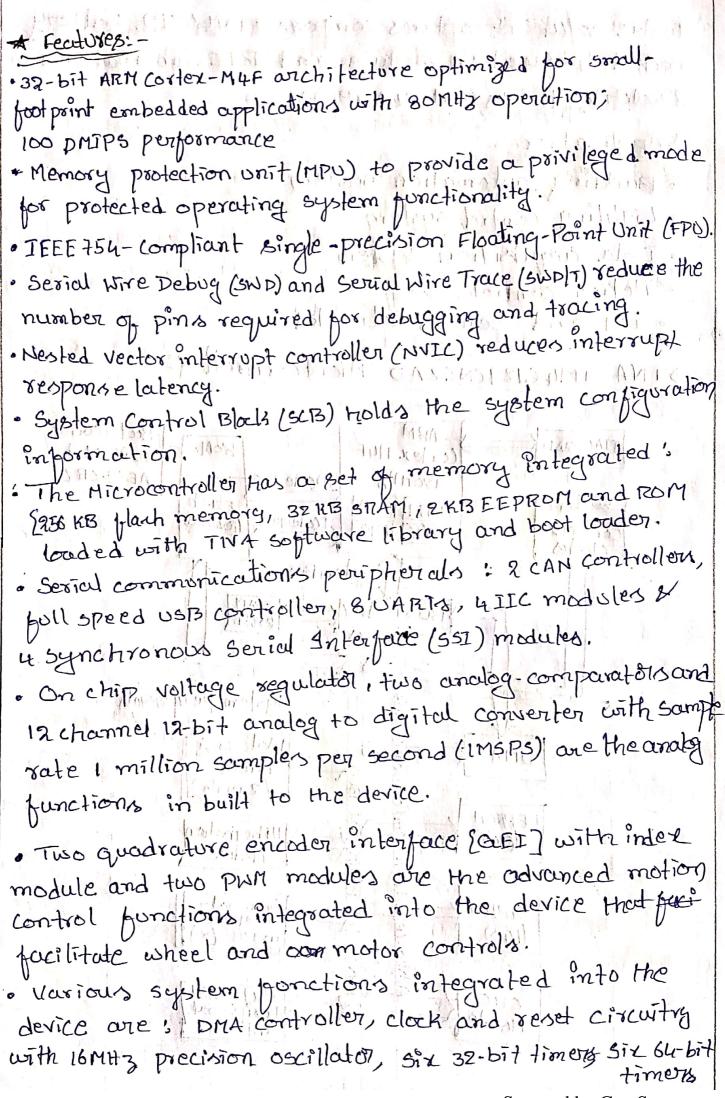

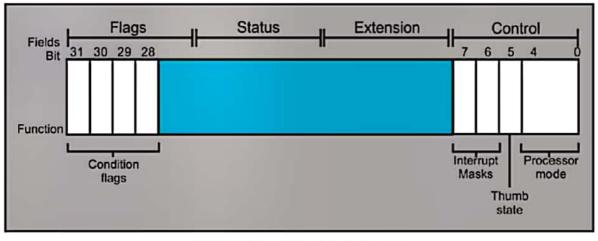

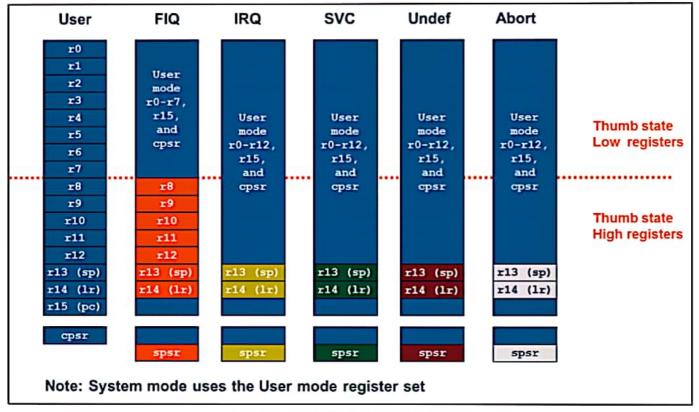

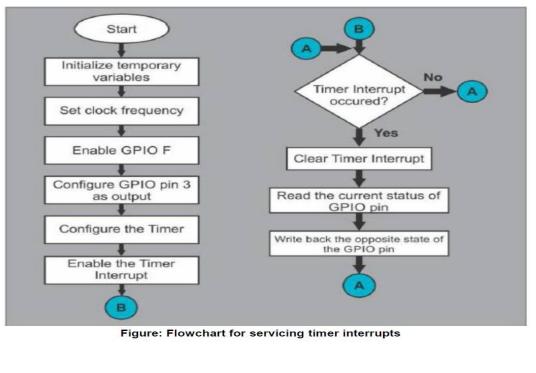

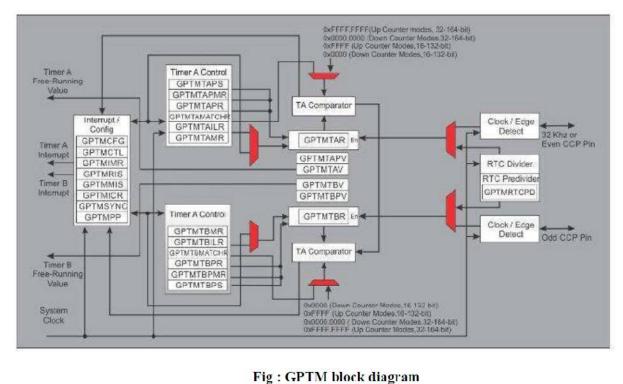

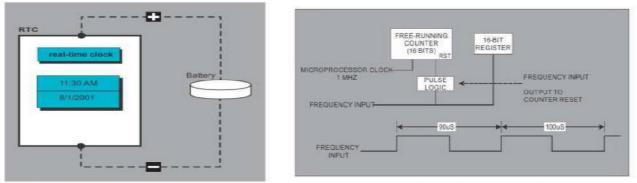

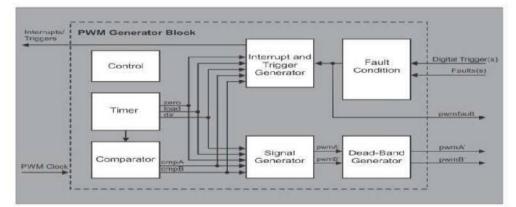

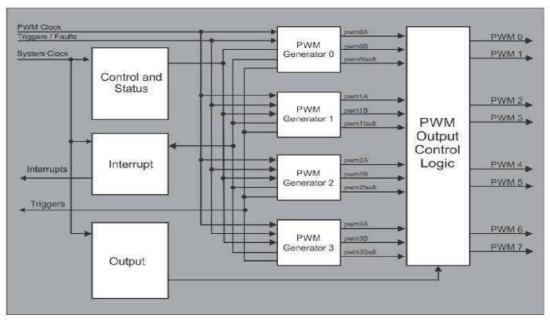

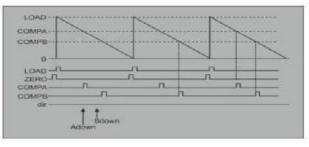

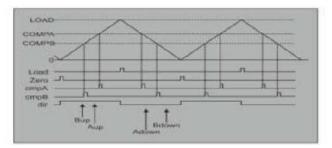

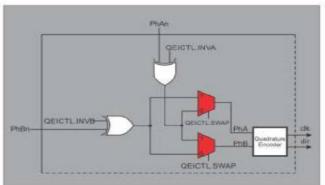

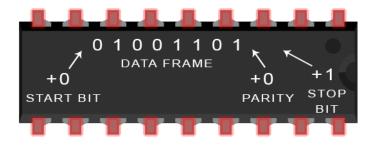

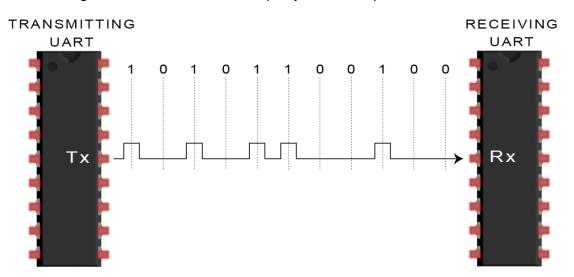

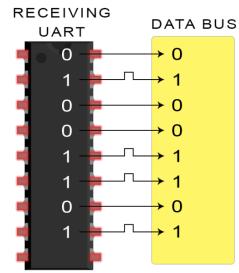

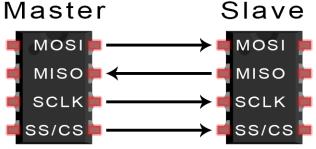

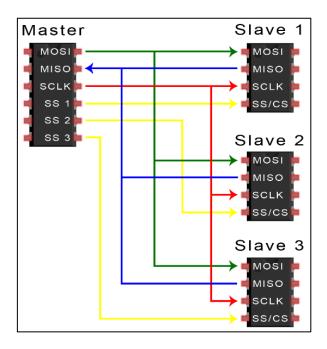

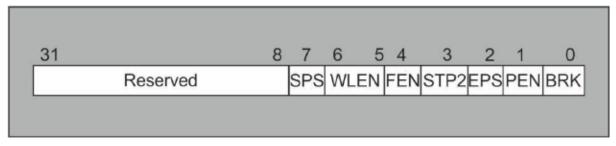

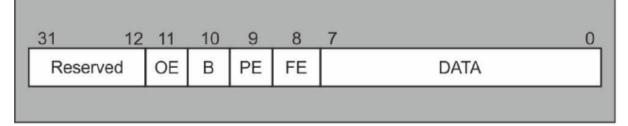

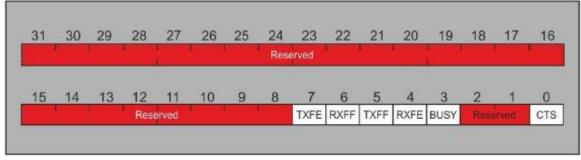

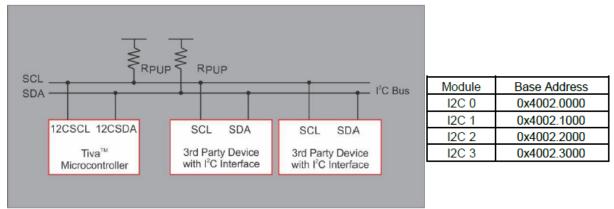

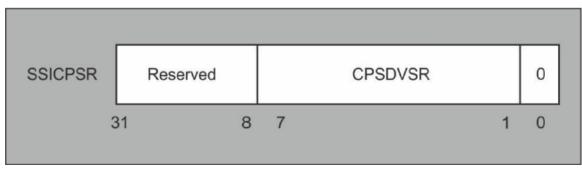

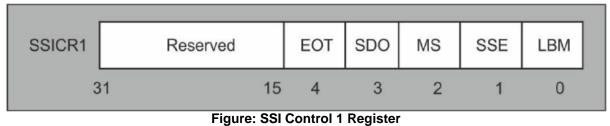

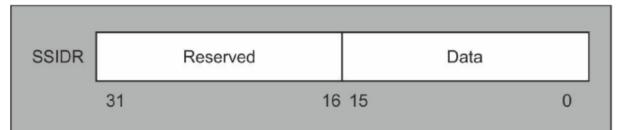

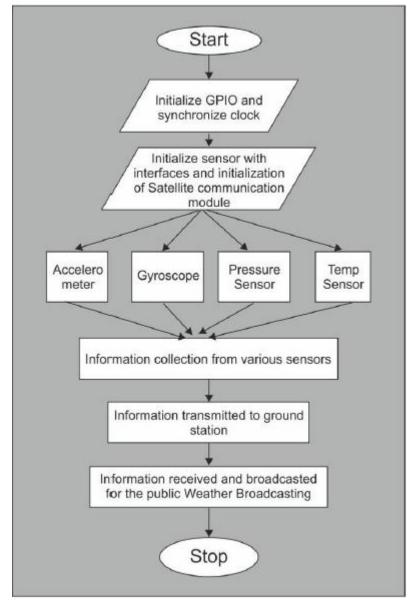

• The 32 bit ALU Performs the arithmetic and logic functions The data in and data out registers hold the input and output data from and to the memory. • The instruction decoder and associated control logic generates approprite control signals for the data path after decoding the fetched instruction. • The MAC unif is to multiply two register operands and accumulate with another register holding the partial som of the products. > The encode Process:-• The encoded instruction byte of the program sourced in the code memory is petched through the data bus and first enters into the data-in register of the ARM architecture from where it is delivered to the instruction decoder. · Appler the instruction is decoded, appropriate control signals are generated for the data path. . The required registers are activated in the register bank and the operand's flow out from the read ports of register bank to the ALU: operand through A-Bus & operanta through BBUS after preproceising at barrel shifter. . The result of operation at AW is return written backto the result, register through a write port at register bank. For Load store instructions, after decoding the instruction the data memory address is pirst calculated at ALU as specified in the instruction and the pointer register is updated at the register bank. . The address in the pointer register is given to the address pregistor to access the memory and transper date. · Ita it is a load multiple 'or store multiple instruction the core does not halt befole completing the required number of data transfers unless it is a reset caception. () daman